- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

Hi everyone,

I am posting this question to clarify my understanding about alternative bank system. Currently I m using t1042 demo board. Nor flash has 2 banks. Bank 0 is default bank and Bank 4 is alternative bank.

As I understood so far, when board have command input from console 'cpld reset altbank', the cpld resets the board and reads RCW, U-boot and other things from the adresses assigned for alternative bank (0xEC000000 for altbank RCW, 0xE8000000 for current bank, refer to documentation)

When I switch to BANK 4(altbank)and write a new U-boot image on its console using Current Bank adress (Not altbank adress), its writing U boot to alternative bank adress because when I send 'cpld reset altbank' command after flashing, board is booting with the u-boot image that I have just flashed onto current bank adress, and when I switch back to BANK 0(which refers current bank), it still has old u-boot image.

The question is, does current bank mean the bank which is in use at the moment, and the alternative bank means the bank which is currently not? If it is, then this means that they are not constant terms?

I messed with memory while flashing some new U boot and RCW with Code Warrior and I think there are some points I miss.

已解决! 转到解答。

I agree that there is some ambiguity in terms "current" and "alternate".

The implementation is as follows:

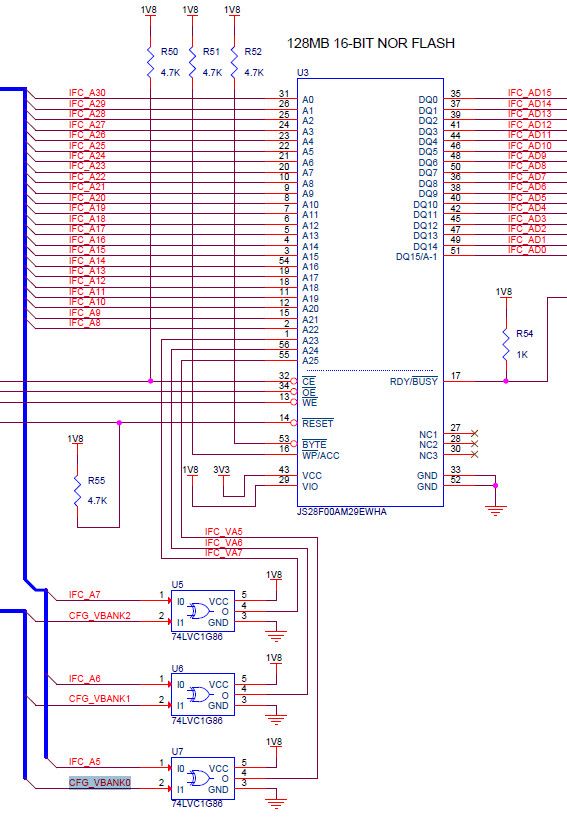

1) CFG_VBANK0 is used to invert MSb of the NOR Flash address to effectively swap the flash halves:

2) Default (again ambiguity :smileywink:) value of the CFG_VBANK0 is selected by SW3[5] and it can be overridden through the CPLD register FLHCSR - refer to the QorIQ T1042D4 Reference Design Board Reference Manual, 3.1.8 Flash control and status register (FLHCSR).

3) U-Boot command "cpld reset altbank" is implemented in the "cpld.c" by calling function "cpld_set_altbank" which enables CFG_VBANK signals override by the CPLD and sets CFG_VBANK0=1 - refer to the sources:

u-boot/T104xRDB.h at b3f98d438eefd1b355efdec0b50af5813ff8d0e1 · qoriq-open-source/u-boot · GitHub

u-boot/cpld.c at b3f98d438eefd1b355efdec0b50af5813ff8d0e1 · qoriq-open-source/u-boot · GitHub

So your understanding:

> does current bank mean the bank which is in use at the moment,

> and the alternative bank means the bank which is currently not?

is correct considering the NOR Flash memory map provided in the QorIQ SDK v2.0-1703 Documentation, NOR Flash memory map:

I agree that there is some ambiguity in terms "current" and "alternate".

The implementation is as follows:

1) CFG_VBANK0 is used to invert MSb of the NOR Flash address to effectively swap the flash halves:

2) Default (again ambiguity :smileywink:) value of the CFG_VBANK0 is selected by SW3[5] and it can be overridden through the CPLD register FLHCSR - refer to the QorIQ T1042D4 Reference Design Board Reference Manual, 3.1.8 Flash control and status register (FLHCSR).

3) U-Boot command "cpld reset altbank" is implemented in the "cpld.c" by calling function "cpld_set_altbank" which enables CFG_VBANK signals override by the CPLD and sets CFG_VBANK0=1 - refer to the sources:

u-boot/T104xRDB.h at b3f98d438eefd1b355efdec0b50af5813ff8d0e1 · qoriq-open-source/u-boot · GitHub

u-boot/cpld.c at b3f98d438eefd1b355efdec0b50af5813ff8d0e1 · qoriq-open-source/u-boot · GitHub

So your understanding:

> does current bank mean the bank which is in use at the moment,

> and the alternative bank means the bank which is currently not?

is correct considering the NOR Flash memory map provided in the QorIQ SDK v2.0-1703 Documentation, NOR Flash memory map:

Hello ufedor,

Thank you for the answer.

> Default (again ambiguity )

Maybe the documentation team can handle with this ambiguities with explanations in next revisions.

I have some questions about this chip select SW3[5].

> 1) CFG_VBANK0 is used to invert MSb of the NOR Flash address to effectively swap the flash halves:

> 2) Default (again ambiguity ) value of the CFG_VBANK0 is selected by SW3[5] and it can be overridden through the CPLD register FLHCSR - refer to the QorIQ T1042D4 Reference Design Board Reference Manual, 3.1.8 Flash control and status register (FLHCSR).

So that, 'cpld reset altbank' command changes the value in FLHCSR register which is already set after power up with SW3[5] value, am I right ?

> is correct considering the NOR Flash memory map provided in the QorIQ SDK v2.0-1703 Documentation, NOR Flash memory map:

So that when I get on BANK 4 and try to write locations tagged with current bank (in documentation) means that I am actually writing to locations tagged with altbank (in documentation) but when I get on BANK 0, current bank adresses really goes in to adresses tagged with current bank ? This speciality is coming from CPLD ?

I know I am giving too many confusing answers but I have a really big problem and trying to figure out how this CPLD works.

Related to my question in this link, [CCS last error: T1040: Core not responding ](CCSProtocolPlugin) error after flashing wrong RCW/wron... In short;

1-) I messed memory of all banks and then I fixed both bank 0 and bank 4 with override RCW method in CodeWarrior.

2-) After this fix, I booted board with Chipselect sw3[5] On (booting with BANK 0), then flashed a working RCW to BANK 4 again with Code Warrior (Meanwhile doing this, I was using ALTBANK RCW adress as offset adres in Target Task).

3-) Bank 4 is crashed and Asleep led was lighting when I try to boot with sw3[5] Off (booting with BANK 4).

4-) I tried to save BANK 4 with the u-boot in BANK 0. But result did not changed. The strange point is, BANK 4 is working with 'cpld reset altbank' command and succesfully boots after I tried to save it with BANK 0. But changing the SW3[5] ping lighting the ASLEEP led.

Do you have any idea about this situation ? Is the Code Warrior causes problem, or the nor flash bank system ?

Extra Information:

I was able to write new U-boot to altbank using Code Warrior. But RCW writing is crashing the bank of given rcw adress.

Long story short:

Code Warrior seems crashing memory of banks when I try to write a new RCW.

> So that, 'cpld reset altbank' command changes the value in FLHCSR register

> which is already set after power up with SW3[5] value, am I right ?

Not correct.

Levels configured by SW3[5:7] are directly translated to CFG_VBANK[0:2] if FLHCSR[BANK_OR]=0

> But RCW writing is crashing the bank of given rcw adress.

What does it mean?

> What does it mean?

Let me explain with examples;

Let say that I booted the board on BANK 4(alternate) and trying to write RCW field of BANK 0 (default). At this point, When I try to write RCW field of BANK 0, Should I use adress offset 0xEC00000 ( referred as alternate bank adress in doc) instead of 0xE8000000(referred as current bank adress in doc) ? With Code Warrior.

Or let say that I booted the board on BANK 4(alternate) and trying to write RCW field of BANK 4 (alternate). At this point, When I try to write RCW field of BANK 4, Should I use adress offset 0xE800000 ( referred as current bank adress in doc ) instead of 0xEC000000(referred as alternate bank adress in doc) ? With Code Warrior.

> Let say that I booted the board on BANK 4(alternate)

How exactly you did that?

Please note that CodeWarrior could reset the board to establish debug connection, so only SW3[5] setting is actual in this case.