- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- ソフトウェア・フォーラム

- :

- プロセッサ・エキスパート・ソフトウェア

- :

- SPIMaster_LDD usage

SPIMaster_LDD usage

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

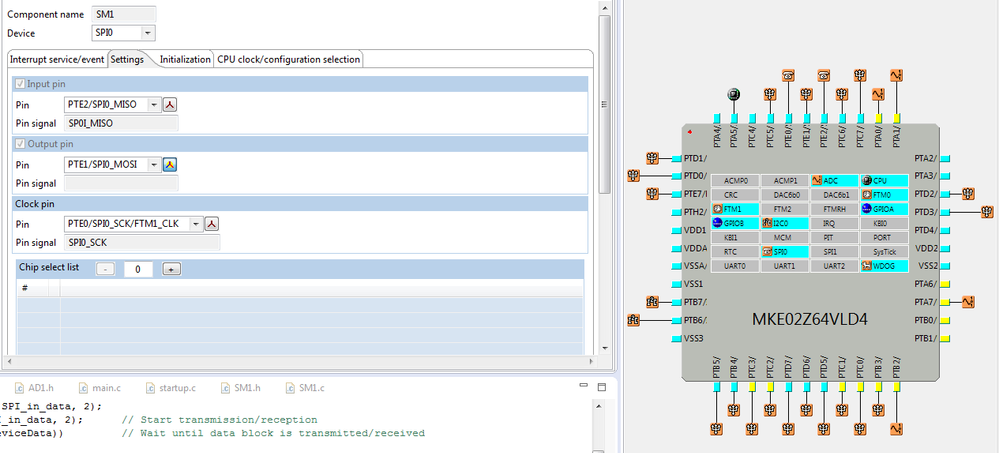

I need to read 2 bytes from one 12-bit ADC using the SPI interface in MKE02Z. I select SPIMaster_LDD from PE and I configure it as shown:

- No Interrupt service/event

- Output pin MOSI not used (I only want to read 2 bytes through MISO)

- No Chip Select is used (I use a GPIO instead)

- Clock rate: 0.5us

- Auto initialization: Enabled

For the driver initialization I do:

SM1_Enable(SM1_DeviceData);

And for reading 2 bytes

Error = SM1_ReceiveBlock(SM1_DeviceData, SPI_in_data, 2);

while (!SM1_GetBlockReceivedStatus(SM1_DeviceData))

SM1_Main(SM1_DeviceData);

The implementation is very easy but... It does not work as I cannot see the 16 clock on SCLK as expected.

Could someone give me a hint?

regards,

gaston

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Gaston,

The MKE02Z derivative provide allocation of all SPI pins based on SPE bit in the SPI Control Register 1. There is not possible do disable allocation of the MOSI pin on this derivative (see the reference manual).

The delay between bytes can be caused by other interrupts routines or by the SPI interrupt routine itself. What is the bus/core clock frequency of the CPU? You can try to use higher core and bus clock frequency.

Best Regards,

Marek Neuzil

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi David,

I see this in the code you've attached:

Error = SM1_ReceiveBlock(MySPIPtr, InpData, BLOCK_SIZE); /* Request data block reception */

Error = SM1_SendBlock(MySPIPtr, OutData, BLOCK_SIZE); /* Start transmission/reception */

But I don't want to send bytes (OutData) through MOSI (pin39, PTE1). Why I have to use a sending function (SendBlock) in order to receive packets (ReceiveBlock)? I don't understand this method. In my application PTE1 is configured as general purpose digital output. If I use the code above, I see unwanted changes on PTE1 because of the SendBlock() function. I've configured this pin as shown here below but the changes on PTE1 persist.

What can I do to solve this?

regards,

gaston

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Gastom,

The SPI device must send and receive data concurrently and the SPI device must send data to receive any data (see the block diagram and functionality description of the SPI in a reference manual). It also means that the ReceiveBlock() method just prepare a buffer to receive data (it does not initiate the receive transfer) and you must use the SendBlock() method to initiate the data transfer (one byte is sent and received concurrently). When you don't use the MOSI pin (the internal signal is not routed on a pin) and the data are not physically transmitted but it does not affect functionality of the SPI device.

Therefore you must use the sequence of ReceiveBlock() and SendBlock() to receive any data.

Best Regards,

Marek Neuzil

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Therefore you must use the sequence of ReceiveBlock() and SendBlock() to receive any data.

Marek, thank you for the clarification

When you don't use the MOSI pin (the internal signal is not routed on a pin) and the data are not physically transmitted but it does not affect functionality of the SPI device.

How can disable the MOSI pin? I'm not able to uncheck it in the component Settings

One more thing. I've tested 2-bytes reception using ReceiveBlock() and SendBlock() as suggested. It works but there is a big gap (8us) between packets (quite big in my opinion). Is it possible to improve this timing?

regards,

gaston

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Gaston,

The MKE02Z derivative provide allocation of all SPI pins based on SPE bit in the SPI Control Register 1. There is not possible do disable allocation of the MOSI pin on this derivative (see the reference manual).

The delay between bytes can be caused by other interrupts routines or by the SPI interrupt routine itself. What is the bus/core clock frequency of the CPU? You can try to use higher core and bus clock frequency.

Best Regards,

Marek Neuzil

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Marek,

I'm afraid I cannot go faster as the bus/core clock is running at 16MHz. Don't worry, so far I can accept the timing between byte packets.

Again, thanks for the given support.

regards,

gaston