- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- パワーマネージメント

- :

- パワーマネージメント

- :

- PF0100 discharge question

PF0100 discharge question

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Customer is doing stress test for their i.MX 6Quad digital cluster which power on PF0100 VIN for 3900ms then off for 100ms repeatedly.

Then found the i.MX 6Quad didn’t power up after 8 hours and can’t reset even set PF0100 PWRON to low then high manually (follow i.MX 6Quad SABRE reset SW2 design).

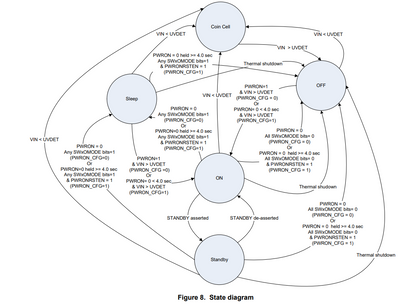

After discuss with NXP PMIC FAE, suspect the cause may because PF0100 didn’t discharge completely, so can't make sure which mode is in state diagram.

Therefore ask customer to measure the discharge time of all output pins which longest is 369ms.

Then NXP FAE ask customer to do more experiments that extend the on-off time.

1. Customer increase on-off period more than 100ms, then found the fail possibility is decreased.

2. Customer increase on-off period more than 500ms, then found the issue didn’t happened after 8 hours.

Customer would like to know why PF0100 can't reset by set PWRON to low then high manually when i.MX 6Quad didn't power up just because it didn't fully discharged?

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Mike,

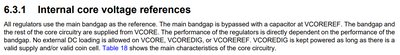

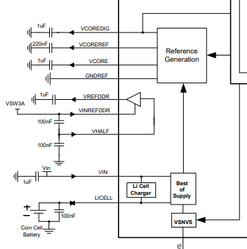

All regulators use the main bandgap as the reference. The main bandgap is bypassed with a capacitor at VCOREREF.

The capacitors on the VCORDIG, VCOREF and VCORE together with the decoupling capacitors on the regulator outputs needs to be discharged to successfully turn off the regulators.

With Best Regards,

Jozef

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Sorry for misleading the issue to PWRON, please allow me to describe issue again.

If customer power on VIN for 3900ms and off for 100ms, then PF0100 will not output voltage after 8 hours.

If cusotmer power on VIN for 3500ms and off for 500ms, then PF0100 will still output voltage after 8 hours.

The longest discharge time of all output pins is 369ms.

Customer would like to know why discharge is not complete, which will affect the situation that PF0100 can't output voltage.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Mike,

All regulators use the main bandgap as the reference. The main bandgap is bypassed with a capacitor at VCOREREF.

The capacitors on the VCORDIG, VCOREF and VCORE together with the decoupling capacitors on the regulator outputs needs to be discharged to successfully turn off the regulators.

With Best Regards,

Jozef

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Where can we find more detail explaination or block diagram or schematic of block of reference gerneration?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

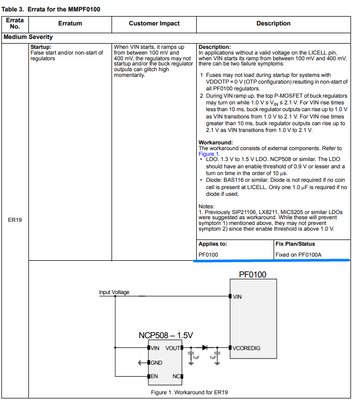

Dear Mike,

I am not sure, if I understand your request. Could you please elaborate? Most of the relevant information can be found in the PF0100 datasheet. Please find additional documents I have found on my PC disk.

With Best Regards,

Jozef

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Mike,

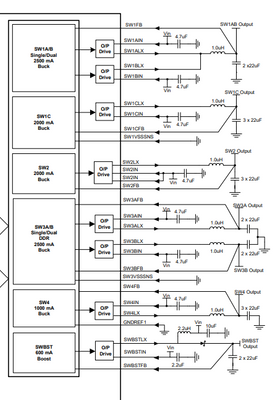

please also check the MMPF0100 Errata. Has the customer the older PF0100 or newer the PF0100A?

With Best Regards,

Jozef

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Mike,

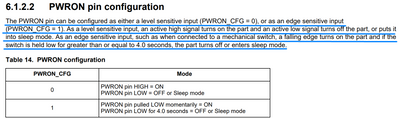

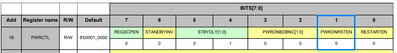

please check how has the customer set the PWRON_CFG bit and the PWRONRSTEN bit.

By default it should be set both of them to 0. The PWRON_CFG to level sensitive.

But if the customer has set the PWRON_CFG to 1, edge sensitive, to properly turn off the PMIC, the PWRON pin must be held low for at least 4s and the PWRONRSTEN must be set to 1. Please refer to the Figure 8. in the MMPF0100 datasheet.

With Best Regards,

Jozef