- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- パワーマネージメント

- :

- パワーマネージメント

- :

- FS4500 SBC FS0b release not worked

FS4500 SBC FS0b release not worked

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

I'm not able to release FS0b pin.Its always low.

Please find the attached snapshots of register values and help me to identify the problem.

Note:In sbc init ,after first watchdog refresh watchdog was disable by selecting watchdog window as 0.

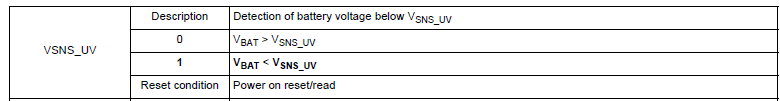

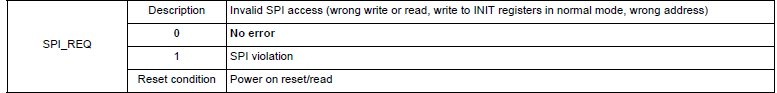

Errors Observed: VSNS_UV=1, FS0B_SNS=0, RSTB_EXT=1, FLT_ERR=6,SPI_REQ=1

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Watchdog disable (WD_WINDOW_3:0 = 0b0000) is effective only when the INIT_FS phase is closed, so it requires at least one good watchdog refresh (0x4D when using a default LFSR value of 0xB2) within the 256 ms of the INIT_FS timeout.

Best regards,

Tomas

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Watchdog disable (WD_WINDOW_3:0 = 0b0000) is effective only when the INIT_FS phase is closed, so it requires at least one good watchdog refresh (0x4D when using a default LFSR value of 0xB2) within the 256 ms of the INIT_FS timeout.

Best regards,

Tomas

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Tomas,Thanks for the reply

Now, I activated periodic watchdog refreshes and FS0b line is released.But still i encountered below errors in driver:

VSNS_UV=1,RSTB_EXT=1,SPI_REQ=1

Input to sbc is always 12v then why VSNS_UV is set?

In Init part of driver ,DIAG_VSUP_VCAN register is readed to clear it ,even though why VSNS_UV is set?.

In which scenarios SPI_REQ bit will be set?

what is the meaning for RSTB_EXT(External) set?

Thanks,

PVR

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

VSNS_UV bit in the DIAG_VSUP_VCAN register is an image of Vbat. After a POR, VSNS crosses VSNS_UV and consequently VSNS_UV flag is set:

As you correctly stated, reading DIAG_VSUP_VCAN register (0x2000) is required after a POR to clear this flag. Are you sure you are reading this register correctly during the initialization phase?

SPI_REQ indicates an invalid SPI access:

Best regards,

Tomas

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

1.Reading DIAG_VSUP_VCAN verified by SPI_G bit and communication was successful.

But some how VSNS_UV was not cleared .

Is there is any other check points?

2.what is the meaning for RSTB_EXT(External) set?