- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- QorIQ Processing Platforms

- :

- P-Series

- :

- Re: p1012: hdlc: when hdlc tx/rx feed with different frequency external clock, rx can not receive data

p1012: hdlc: when hdlc tx/rx feed with different frequency external clock, rx can not receive data

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

p1012: hdlc: when hdlc tx/rx feed with different frequency external clock, rx can not receive data

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I encounter a very strange issue about HDLC.

For the HDLC, in my design, uses external clock,

during debug, find that, if feed the HDLC's rx/rx clock with different frequency clock, HDLC rx channel

will can not receive data any more.

Does it need to do some special setting for HDLC if RX/TX clock is different frequency?

Could you help to give some suggestions?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Could you please draw the exact connection circuit of both sides P1012 and remote device, and both TX and RX side, and show how exactly (from which source) the clock is applied for all four cases (P1012tx, P1012rx, remote tx, remote tx).

Have a great day,

Alexander

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Alexander,

Thanks a lot!

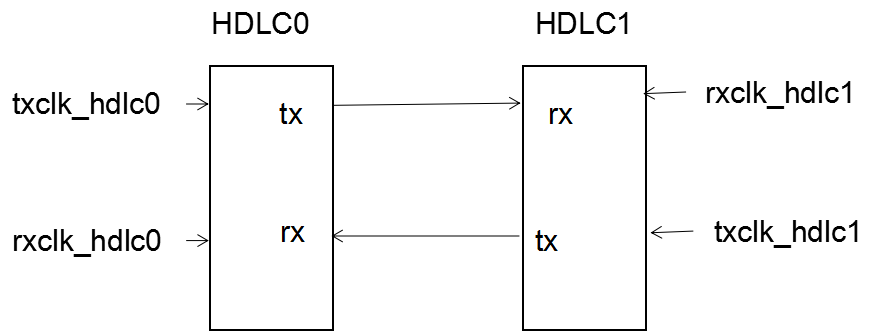

I use the different HDLC peripherals of the same P1021 chip to communicate. The connection relationship is as below:

As the above figure said:

txclk_hdlc0, rxclk_hdlc1: 8M

rxclk_hddlc0, txclk_hdlc1: 16M

we have done the below experiments:

1) use 16M clock to communicate

That is, HDLC1 send and HDLC0 receive, there are only send interrupt and no receive interrupt, receive side

can not receive data;

2) use 8M clock to communicate

That is, HDLC0 send and HDLC1 receive, there are send interrupt and receive interrupt, but the receive side

will pop out error in the BD status field.

Thank you!

Carl

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorre, the figure is not clear, please answer following questions.

1. Please confirm txclk_hdlc0 and rxclk_hdlc1 is the same clock, sourced from the same (one) clock source.

2. Please confirm rxclk_hddlc0 and txclk_hdlc1 is the same clock, sourced from the same (one) clock source.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Alexander,

yes,

1. Please confirm txclk_hdlc0 and rxclk_hdlc1 is the same clock, sourced from the same (one) clock source.

yes, txclk_hdlc0 and rxclk_hdlc1 is from the same crystal oscillator with 8M frequency.

2. Please confirm rxclk_hddlc0 and txclk_hdlc1 is the same clock, sourced from the same (one) clock source.

yes, rxclk_hddlc0 and txclk_hdlc1 is from the same crystal oscillator with 16M frequency.

Thanks a lot

Carl