- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- QorIQプロセッシングプラットフォーム

- :

- Pシリーズ

- :

- Re: P1010 IFC_RB_B usage

P1010 IFC_RB_B usage

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

P1010 IFC_RB_B usage

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I'm trying to access a peripheral device I have attached to IFC CS3_B on my P1010.

The peripheral drives an active low wait signal when it needs to extend the access.

I have the wait output attached to the IFC_RB_B input, it looks to me like the IFC is ignoring the signal.

I currently have CS3 configured in NOR mode, as in GPCM mode the pin acts in the opposite sense to terminate an access quickly (which I can see occurring).

P1010RM.pdf Table 12-1 (page 508) suggests that IFC_RB_B input is the "NOR Ready Busy Input"

Am I missing something here? Do I need to enable something to get the Chip select to take note of the signal?

Regards,

stu

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Please provide values of all IFC registers and digital scope trace(s) showing the IFC transaction with IFC_RB_B.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

CS0 = 16-bit NOR boot flash

CS1 = 16-bit NAND flash

CS2 = unused

CS3 = 8 bit peripheral

Registers are:

IFC Controller Registers

CSPR0:0xEF000105 AMASK0:0xFF000000 CSOR0:0x0000E001

IFC_FTIM0:0x10020001

IFC_FTIM1:0x14001400

IFC_FTIM2:0x0118000E

IFC_FTIM3:0x00000000

CSPR1:0xFF800103 AMASK1:0xFFFF0000 CSOR1:0x85082105

IFC_FTIM0:0x04050404

IFC_FTIM1:0x011A090A

IFC_FTIM2:0x0120201E

IFC_FTIM3:0x00000000

CSPR2:0x00000000 AMASK2:0x00000000 CSOR2:0x0000000C

IFC_FTIM0:0x00000000

IFC_FTIM1:0x00000000

IFC_FTIM2:0x00000000

IFC_FTIM3:0x00000000

CSPR3:0xFFB00081 AMASK3:0xFFFF0000 CSOR3:0x01020000

IFC_FTIM0:0x10020401

IFC_FTIM1:0x07001E0E

IFC_FTIM2:0x0610181F

IFC_FTIM3:0x00000000

IFC_CCR: 0x07000000

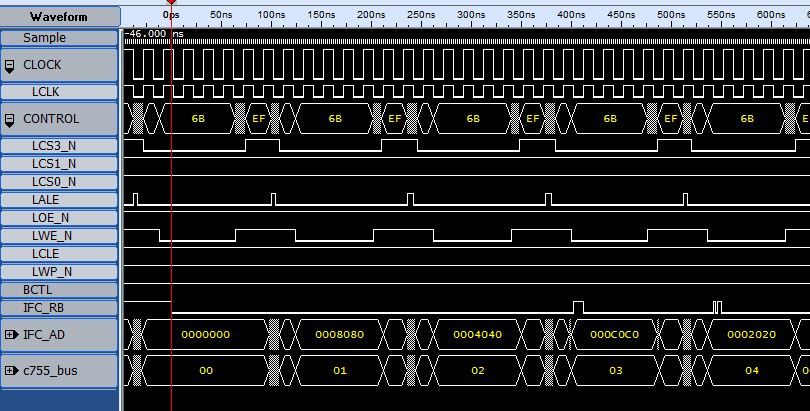

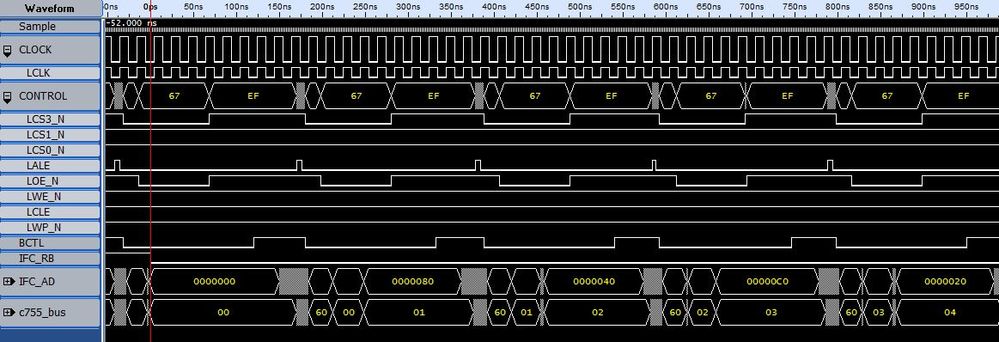

writing a sequential value:

reading it back:

c755_bus is the lower 8 bits of the IFC_AD bus bit swapped.

I triggered the analyser on WAIT going low. The peripheral drives WAIT off the falling edge of IFC_LCLK @50Mhz

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

The state of IFC_RB_B is reflected in “Ready busy status for each chip-select (IFC_RB_STAT)”, there is no other use of this signal. The “Ready busy status for each chip-select (IFC_RB_STAT)” could be used according to specific software design.

Q) Does it mean that IFC_RB_B can't be used to extend the NOR FCM transaction in any way?

A) Yes. It cannot be used to extend the NOR FCM transaction in any way.