- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- Other NXP Products

- :

- Re: S32R45 board, how to drive PCIE work?

S32R45 board, how to drive PCIE work?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

S32R45 board, how to drive PCIE work?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi,

We designed our own hardware board based on S32R45, Currently, pcie debugging encounters some problems, hope your help, thank you!

S32R45 SoC has two SerDes modules (0 and 1), each of them with one PCIe controller. Now, let me address the two main issues(only target at PCIE1 below):

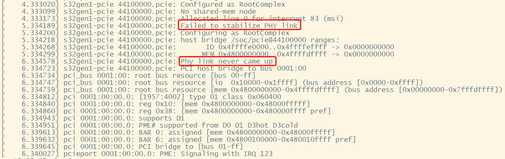

1. Failed to stabilize PHY link(ssd card has been inserted)

2. The internal 100MHz reference clock could not be detected by oscilloscope.

Attention:

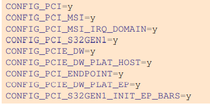

1. I configed pcie to RC mode.

2. we used R45 internal 100MHz reference clock.

3. uboot start command

4. linux pcie config

Otherwise, phy link nerver came up, primary cause may be 100MHz internal clock missing. From my perspective, R45 internal 100MHz(PCIE1_CLK_P/PCIE1_CLK_N) always exists after being powered on, why be gone.

Looking forward to your reply!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Could you please share name of your company? I need it to be able ask RADAR team.

Best regards,

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thans for your reply.

Our company information is as follows, Beijing Muniu Pilot Technology Co., LTD, focus on the development and production of millimeter wave radar products.

In addition to the problems mentioned earlier, I want to emphasize this issue:

1. PCIE0/1_CLK_P/N clock pin of S32R45, whether it can be output to peripherals as a 100M reference clock(eg, PCIe SSD).If that' okay, Is there any special parameter configuration required on the software?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Sorry for the delay! Can you provide the BSP version you are using as reference? and if possible share portions of the schematics related to the PCIe module?

Is the device detected in Uboot? Can you share the entire log too?

Best Regards,

Alejandro