- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

Problem at setting FTM0 Clock source to SPLL DIV1 CLK using Kinetis MKE18F512

Hello

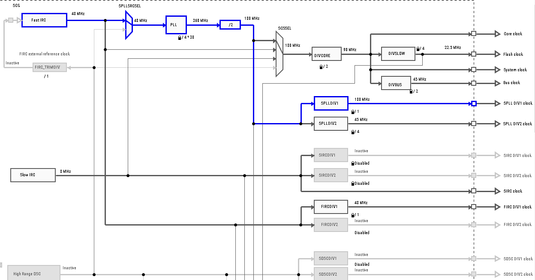

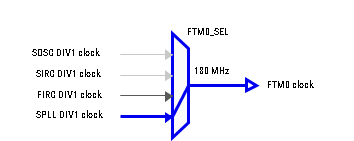

I am using fast IRC clock configuration to get 180Mhz clock connected to the FTM0 clock source.

but when starting FTM0 by FTM0 Clock:

FTM_StartTimer(IFTM_PERIPHERAL, kFTM_FixedClock);

the timer dose not startup.

when starting FTM0 by System Clock:

FTM_StartTimer(IFTM_PERIPHERAL, kFTM_SystemClock);

the timer starts with no problem.

I need to run FTM0 by FTM0 180Mhz clock derived from the SPLL.

what could the problem be ?

Hi @JohnEE

I hope you are doing well during quarantine times.

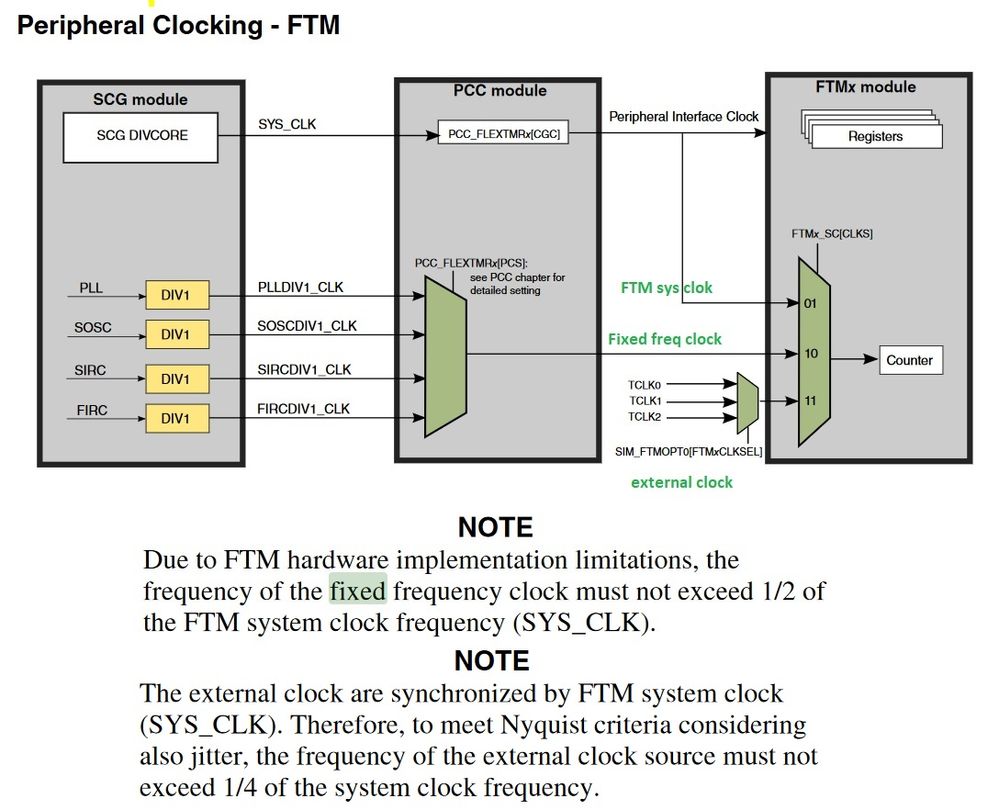

According to the KE1xx Reference Manual section 41.1.2 FTM Clocking Information ,the fixed clock frequency shall not exceed 1/2 of the FTM system clock frequency.

Apparently, in your configuration, the fixed clock is greater than the FTM system clock. So, this seems to be the root of the issue.

On the other hand the FTM sysclock is not able to reach 180 MHz frequency neither. Since the maximum frequency of SYS_CLK (from where FTM sysclok is derived) is 168 MHz Further details in section 18.3Clock definitions of the RM

I hope this helps,

If you have any comments ,please, let me know.

Regards,

Diego.