- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

the window mode of MPC5748G,CMP module

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Sir or Mandam,

I have encountered some problem when configuring window mode of MPC5748G, CMP module.

Attached is my test project. I have used CMP_0 module, the positive input is the voltage that I give through PG7, the negative input is set to 3.3V through DAC, the output pin is PC10, and its voltage will change with the result of comparision. When the voltage of PG7 is higher than 3.3V, LED2 is turned on, and PC10 is high. When the voltage of PG7 is lower than 3.3V, LED1 is turned on, and PC10 is low.

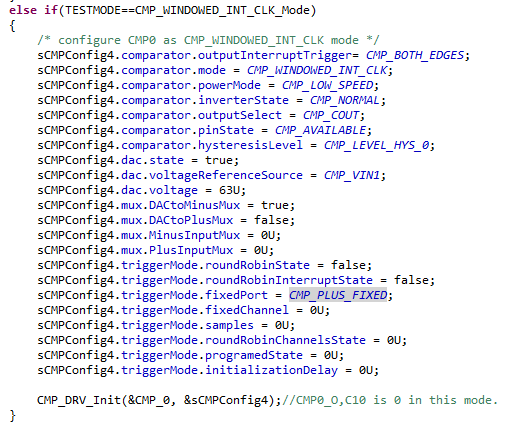

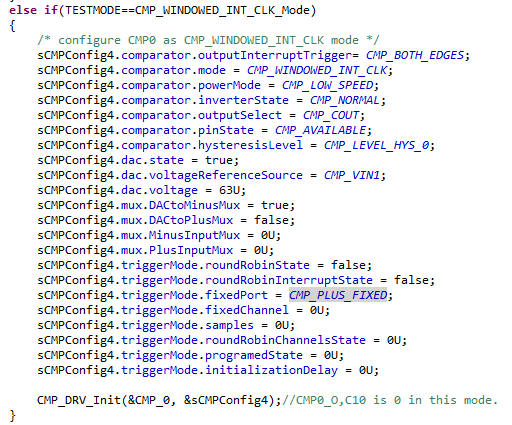

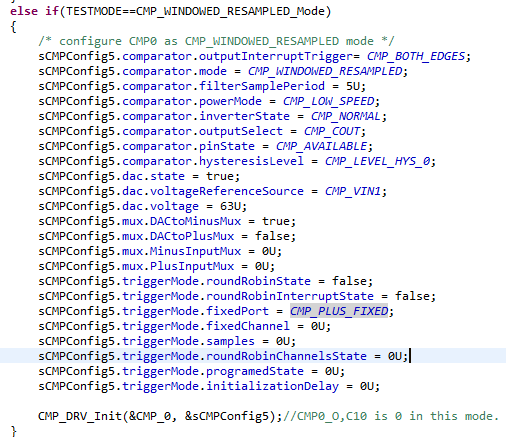

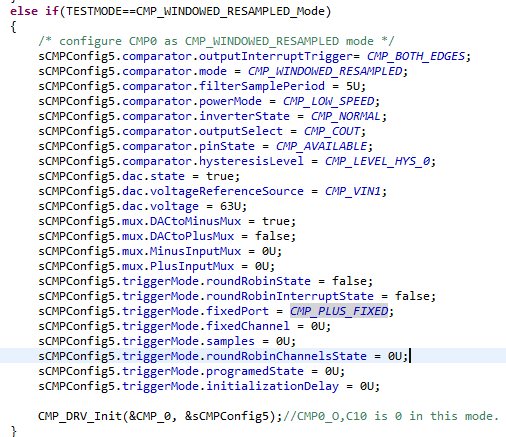

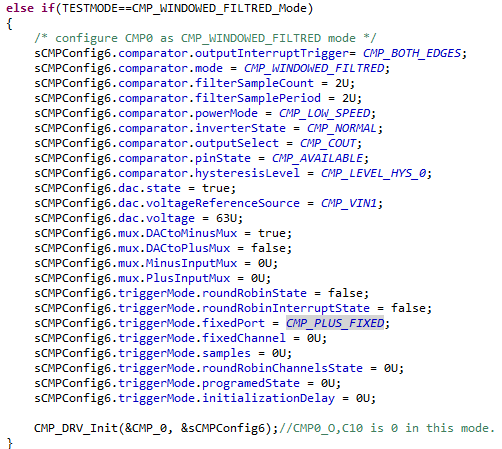

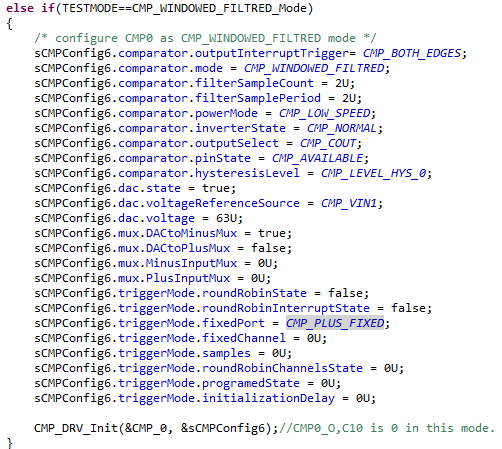

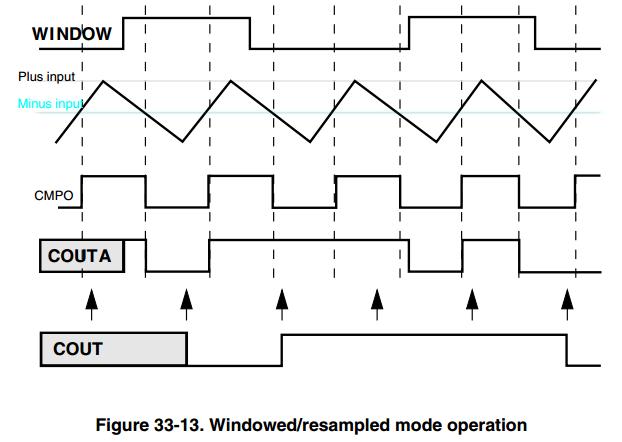

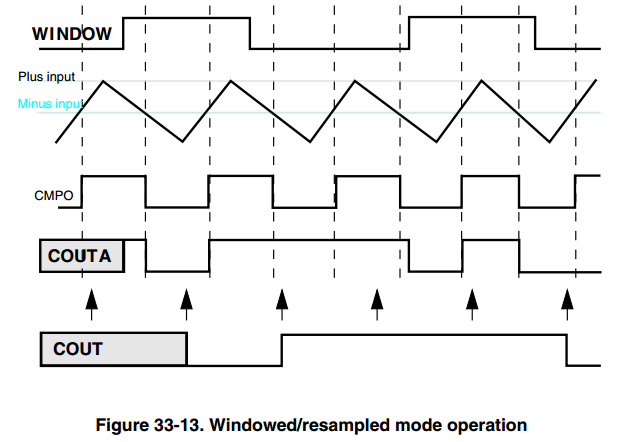

In test_demo.c, when the input of PG7 is a square wave of 5V, 50Hz, 50% duty, why is the output wave of PC10 in CMP_WINDOWED_INT_CLK_Mode, CMP_WINDOWED_RESAMPLED_Mode and CMP_WINDOWED_FILTRED_Mode always low?

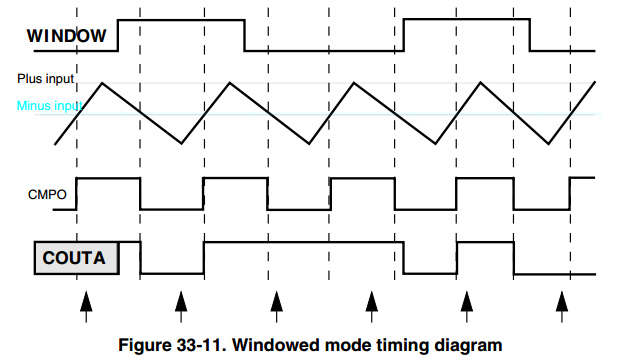

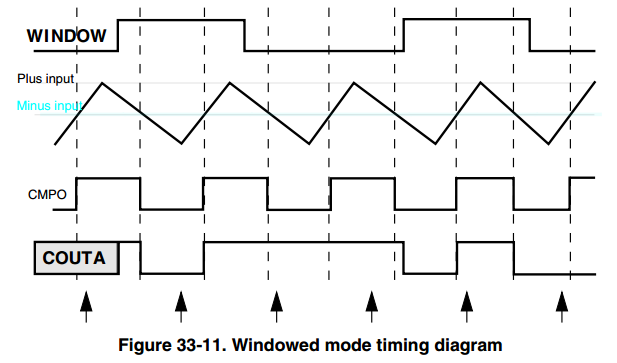

What should I do if I want to get the following output wave?

Could you please help me to find out what mistake I have made, and how to configure correctly these three modes with window?

Thank you very much for your help!

Yours sincerely,

QIAN Shifei

Original Attachment has been moved to: mpc5748g_Z4_1.rar

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I tested your code in CMP_WINDOWED_INT_CLK_Mode on MPC5648G EVB. I connected trimmer (TP18) to pin PG7 and measure CMP0_O on PC10 pin (J14.1). I see PC10 toggling if adjusting the trimmer. COUT bit in CMP.C0 is also set/cleared. It is also working with the square wave you have on PG7.

Just to be able to read the PC10 pin back you need to set IBE bit of the MSCR[42], thus result2 variable will be also updated.

Also you set DAC output to 3.3V, so be sure your analog input is above this threshold to see COUT set. I can recommend to set DAC output lower, for example in the middle of the range, i.e. 1.65V.

Note: the WINDOW signal in the window mode of the CMP is controlled via the GPR register bits in the device.

Refer to GPR_CTL[CMP_ACT_SAM] and GPR_CTL[CMP_SAMP_SEL] registers for details.

So if GPR_CTL[CMP_SAMP_SEL] = 1 then GPR_CTL[CMP_ACT_SAM] bit represents WINDOW/SAMPLE signal.

If GPR_CTL[CMP_SAMP_SEL] = 0 then RTC clock goes to WINDOW/SAMPLE signal.

By default GPR_CTL[CMP_SAMP_SEL]=0, thus RTC clock is used as WINDOW/SAMPLE signal. Check which clock is selected in the RTC module, maybe the source clock is not active.

Or set both the GPR_CTL[CMP_ACT_SAM] and GPR_CTL[CMP_SAMP_SEL] to make WINDOW = 1.

BR, Petr