- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

i use dma transfer data from source --> destination,the program lists below.(See appendix for detailed code)

the question was caused by "dly = destination[10]; "

if there is no read of destination[], for example use "dly = 100" instead of " dly = destination[10]; " this program will work well

about dly = destination[X]; if X< 8 it seems that the first 8 data of destination[] cannot be update by dma

if X>=8 it seems that the last 8 data of destination[] cannot be update by dma (PS: i am not try every index)

Thank you very much!

uint32_t source[16]={1,2,3,4,5,6,7,8,9,10,11,12,13,14,15,16};

uint32_t destination[16]={0,0,0,0, 0,0,0,0, 0,0,0,0, 0,0,0,0};

__attribute__ ((section(".text")))

int main(void)

{

uint32_t k,counter = 0;

uint32_t dly;

xcptn_xmpl (); /* Configure and Enable Interrupts */

CLK_Init();

AIPS_0_Init();

DMA_0_Init();

for(;;)

{

dly = destination[10]; /*this will cause strange phenomenon*/

for(k=0;k<dly;k++);

//SoftTrig DMA

DMA_0.TCD[0].CSR.B.START = 1u;

while(DMA_0.TCD[0].CSR.B.DONE == 0u){};

DMA_0.TCD[0].CSR.B.DONE = 0u;

for(k=0;k<100000;k++);

/*update the source data */

for(k=0;k<16;k++)

{

source[k] = counter;

}

counter++;

}

return 0;

}

Original Attachment has been moved to: Example_Base.c.zip

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

i find "disable dcache" before for(;;) can solve this problem

i wander why? Is there any document about how to use cache? Thank you very much!

void dcache_disable(void)

{

register uint32_t val;

E200CORE_SPR_GET(val,E200CORE_L1CSR0); /* L1CSR0 */

val &= ~E200CORE_L1CSR0_CE;

/* Memory Synchronize */

E200CORE_SYNC();

/* Instruction Synchronize */

E200CORE_ISYNC();

E200CORE_SPR_SET(E200CORE_L1CSR0,val);

/* Instruction Synchronize */

E200CORE_ISYNC();

}

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

i find "disable dcache" before for(;;) can solve this problem

i wander why? Is there any document about how to use cache? Thank you very much!

void dcache_disable(void)

{

register uint32_t val;

E200CORE_SPR_GET(val,E200CORE_L1CSR0); /* L1CSR0 */

val &= ~E200CORE_L1CSR0_CE;

/* Memory Synchronize */

E200CORE_SYNC();

/* Instruction Synchronize */

E200CORE_ISYNC();

E200CORE_SPR_SET(E200CORE_L1CSR0,val);

/* Instruction Synchronize */

E200CORE_ISYNC();

}

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

using cache together with DMA causes this issue. Explanation is fairly simple. When some lines of RAM are cached, debugger reads this lines via core and it finds the data at first in cache. When there is cache hit (line of RAM is present in cache), data are read from cache memory instead of RAM memory. But DMA writes data directly to the RAM. This causes inconsistencies between data in RAM and cache. There are different data in RAM and different data in cache.

You should mark the part of RAM, which is used for DMA transfers as non-cacheable.

Please look at the following document, which could be helpful for you:

e200 Core Training relevant to MPC55xx and MPC56xx device family

Regards,

Martin

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

"You should mark the part of RAM, which is used for DMA transfers as non-cacheable."

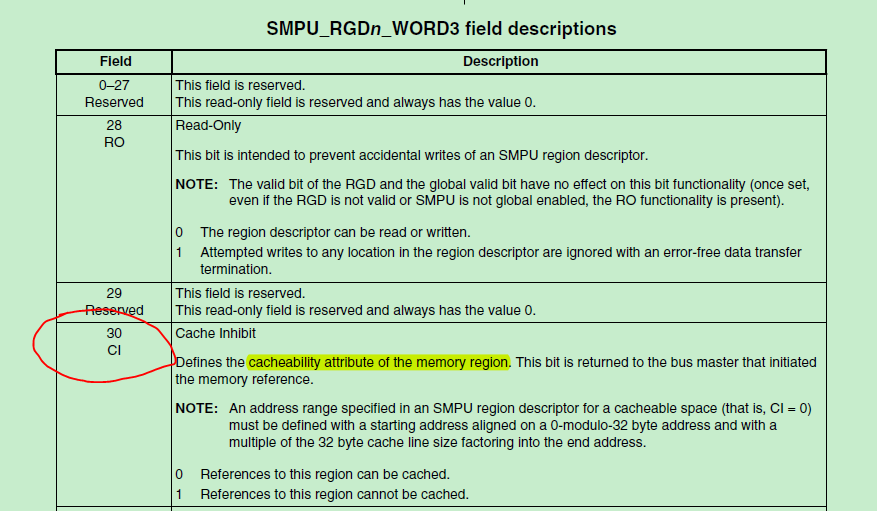

------------- Is this configure SMPU_RGDn_WORD3.CI bit? Thank you!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

yes, this is the correct way.

Regards,

Martin

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

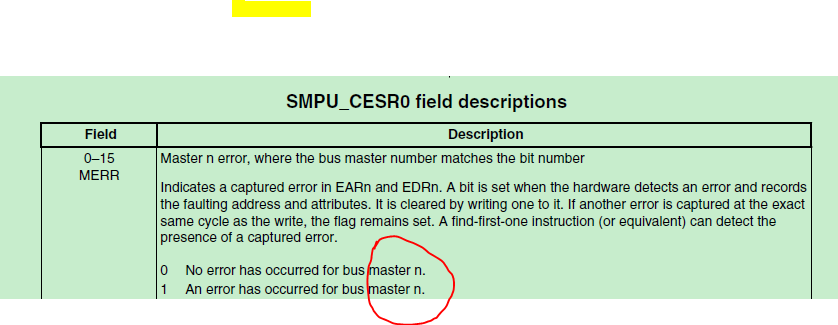

i read the smpu chapter and find that it mentioned the "master n" i wonder what is the "master n"? thank you very much!

which(below) is the "master n"?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

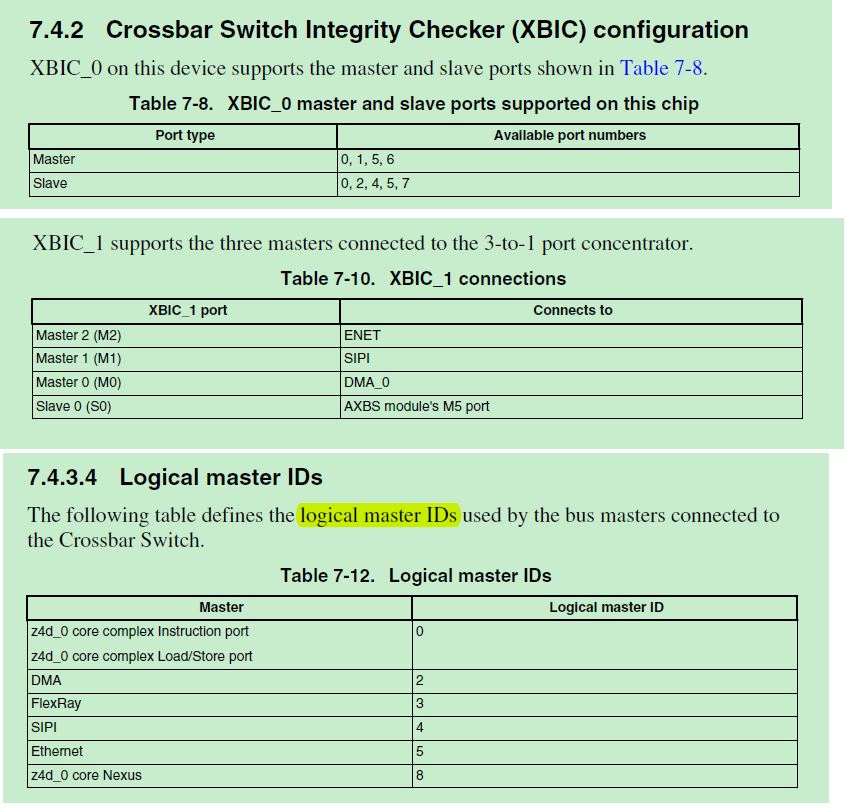

the n means the logical master ID. For example master 2 is DMA, master 3 is FlexRay and so on, see table 7-12

Regards,

Martin