- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

machine check exception after generating multi bit error (MPC5777C) while testing SRAM

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

I've been working on EIM_ERM module lately. I could see that a machine check exception occurs after generating a multi bit error. Although I've tried to handle the exception by writing a logic which instructs to move to next instrcution. Surprisingly,the next instruction also goes into handler and then the process repeats.I tried disabling the global enable and bit in EIMCR also. Below is the handler:

void machine_exception(VectorId vector,const void *stack_ptr)

{

MPC::ErrorInjectionModule eim(0xFFF64000UL);

Uint32 new_xsrr0 = 0UL;

eim.disable_injection();

new_xsrr0 = get_xsrr0((Uint32 *)stack_ptr, std_context_size) + 4UL;

set_xsrr0((Uint32 *)stack_ptr, std_context_size, new_xsrr0);

return;

}

PFA of the registers after exception has occured

Kindly let me know if I am going wrong somewhere.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

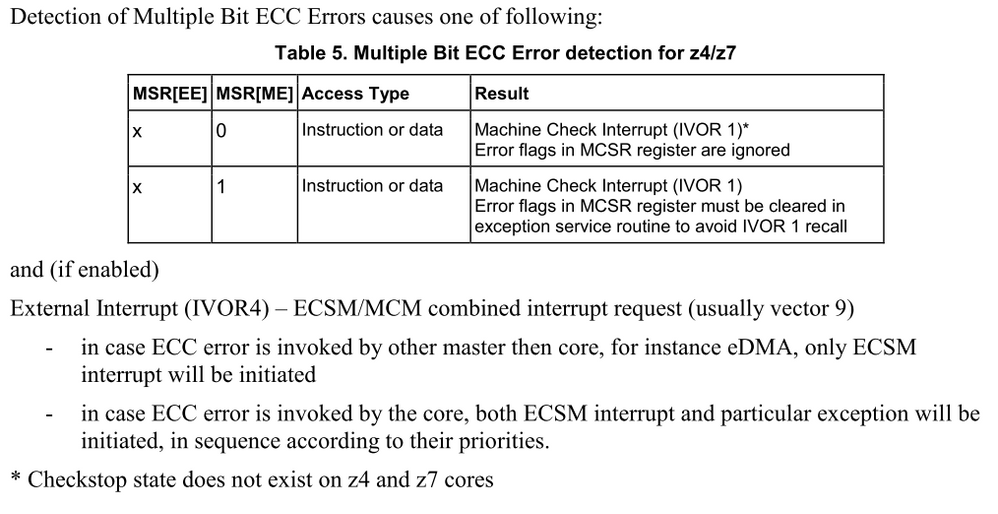

After injecting the multibit ECC fault to RAM:

So, once you inject ECC multibit error you have to care about IVOR1 or 0. Depends on your micro settings.

If you do not serve it the device will be reset.

For correct servicing please refer to chapter 5 -> Non-correctable ECC error servicing

of application note:

https://community.nxp.com/docs/DOC-103300

regards,

Peter