- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Re: Write to 5644 CRC Module register causes processor exception

Write to 5644 CRC Module register causes processor exception

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

With 5644A, writing to CRC_CFG register causes a processor exception.

Using the definition of CRC in mpc5644a.h, at address 0xFFE68000

// For example...

CRC.CFG.B.POLY = 0;

Causes a processor exception. What could be wrong?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

the problem is that CRC registers are not covered by default MMU settings. So, access to the registers leads to bus error and to exception (IVOR1).

Add the following code to your project and it will work. It just creates new MMU page that covers area 0xFFE0_0000 - 0xFFEF_FFFF.

//MMU - TLB6

asm

{

lis r3, 0x1006

mtmas0 r3

lis r3, 0xC000

ori r3, r3, 0x0500

mtmas1 r3

lis r3, 0xFFE0

ori r3, r3, 0x000A

mtmas2 r3

lis r3, 0xFFE0

ori r3, r3, 0x003F

mtmas3 r3

tlbwe

}

Regards,

Lukas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks. Could you please point to where this is documented?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

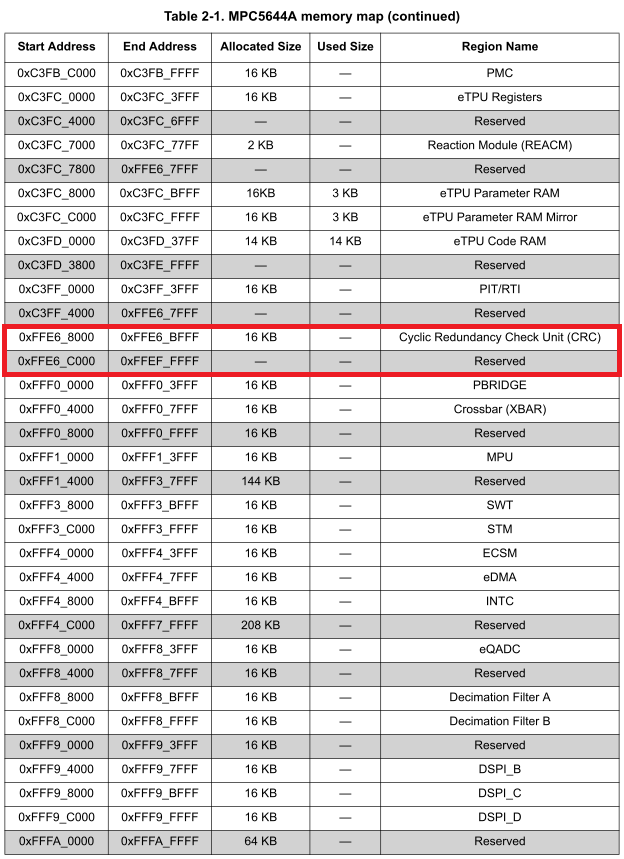

the MMU is initialized by BAM code which resides in ROM memory. The same BAM code is used on more devices (not only MPC5644A) for compatibility reasons and also to avoid risk when changing the code. Unfortunately the default MMU settings do not cover CRC module because it is outside the MMU page covering Peripheral Bridge B.

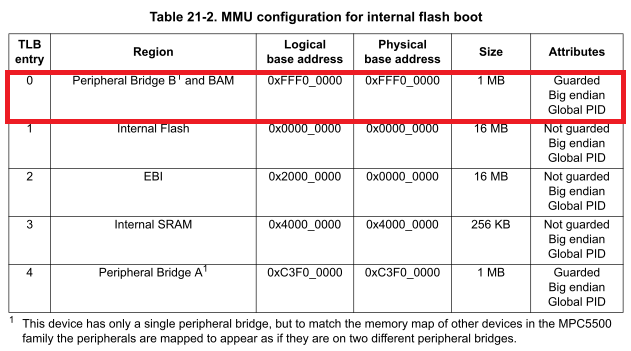

The default MMU settings are:

But here you can see that CRC module is not covered by TLB entry 0:

So, it is necessary to adjust the MMU settings...

Regards,

Lukas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

the problem is that CRC registers are not covered by default MMU settings. So, access to the registers leads to bus error and to exception (IVOR1).

Add the following code to your project and it will work. It just creates new MMU page that covers area 0xFFE0_0000 - 0xFFEF_FFFF.

//MMU - TLB6

asm

{

lis r3, 0x1006

mtmas0 r3

lis r3, 0xC000

ori r3, r3, 0x0500

mtmas1 r3

lis r3, 0xFFE0

ori r3, r3, 0x000A

mtmas2 r3

lis r3, 0xFFE0

ori r3, r3, 0x003F

mtmas3 r3

tlbwe

}

Regards,

Lukas