- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

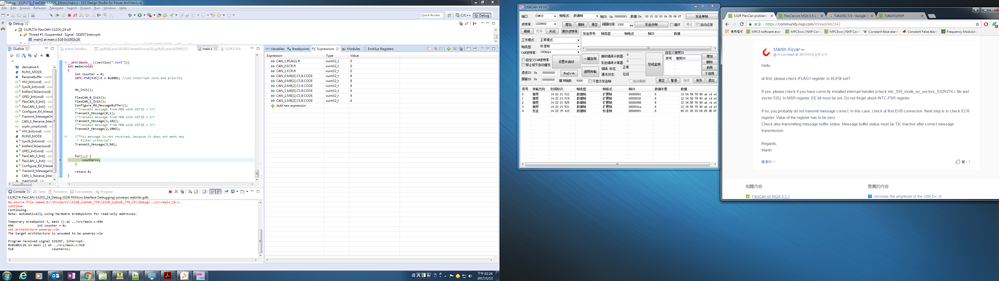

S32R FlexCan problem

Hi,

I'd like to try FlexCan function on S32R EVB.

I found Example MPC5775K FlexCAN_with_interrupts_v1.1 S32DS .

I Check S32R274_IO_Signal_Description_and_Input_multiplexing_tables_Rev2,

It seems the same IO between S32R and 5775K.

So I only modified S32R timing in inital.

But it not work.

I saw 5775K set CAN_CLK at 66MHz, but S32R set CAN_CLK at 40 MHz.

Does it matter?

Yi-Lin

Original Attachment has been moved to: S32R_Cubtek_77G.zip

Hello,

Follow your suggestion:

I runExample S32R274 FlexCAN_with_Interrupts S32DS.

I can see the TX message output and I send single frame.

I check CAN_1.IFLAG1.R = 0 mean BUF0I isn't set.

Both of can0 and can1 ECR = 0;

and Message buffer status are inactive.

How to check EVB connection?

I check R156 on EVB. and it get the signal.

Are there any check points I can try?

Hi Martin,

I modified the extended ID to 0,1,2.

and try to send data ID with 0, 1.

But CAN_1.IFLAG1.R is still 0;

Is some thing wrong?

static void Configure_RX_MessageBuffer(void)

{

CAN_1.MB[0].CS.B.CODE = 0x0; //MB inactive

CAN_1.MB[0].CS.B.IDE = 1;

CAN_1.MB[0].ID.R = 0; //set extended ID

CAN_1.MB[0].DATA.W[1] = 0x00000000; //data1 set (optional)

CAN_1.MB[0].DATA.W[0] = 0x00000000; //data0 set (optional)

CAN_1.MB[0].CS.B.CODE = 0x4; //MB empty - ready for receive

CAN_1.MB[1].CS.B.CODE = 0x0; //MB inactive

CAN_1.MB[1].CS.B.IDE = 1;

CAN_1.MB[1].ID.R = 1; //set extended ID

CAN_1.MB[1].DATA.W[1] = 0x00000000; //data1 set (optional)

CAN_1.MB[1].DATA.W[0] = 0x00000000; //data0 set (optional)

CAN_1.MB[1].CS.B.CODE = 0x4; //MB empty - ready for receive

CAN_1.MB[2].CS.B.CODE = 0x0; //MB inactive

CAN_1.MB[2].CS.B.IDE = 1;

CAN_1.MB[2].ID.R = 2; //set extended ID

CAN_1.MB[2].DATA.W[1] = 0x00000000; //data1 set (optional)

CAN_1.MB[2].DATA.W[0] = 0x00000000; //data0 set (optional)

CAN_1.MB[2].CS.B.CODE = 0x4; //MB empty - ready for receive

}

Hello,

what do you actually try to do? Do you communicate between CAN modules on EVB or you try to communicate between CAN module and PC? I saw an application in one of your post above.

The example I sent you works correct if you connect CAN modules according to the example description. If you try to communicate with PC, please check your application settings.

Without RX masking it does not matter what are the IDs in message buffer, but you must set standard or extended IDs on both sides. The code you posted above sets IDs as extended.

Regards,

Martin

I try to communicate between CAN and PC.

And yes, it's connection problem.

It's work now.

Thanks for your help.

It can transmit now.

But It can't trigger interrupt when receive.

Any suggestion?

Hello,

at first, please check IFLAG1 register. Is BUF0I set?

If yes, please check if you have correctly installed interrupt handler (check intc_SW_mode_isr_vectors_S32R274.c file and vector 535). In MSR register, EE bit must be set. Do not forget about INTC.PSR register.

If no, you probably do not transmit message correct. In this case, check at first EVB connection. Next step is to check ECR register. Value of the register has to be zero.

Check also transmitting message buffer status. Message buffer status must be TX: Inactive after correct message transmission.

Regards,

Martin

Hi,

there is not any difference in FlexCan bit timing, because in both cases 40MHz crystal is used. But there is a difference in signal routing on daughter cards.

I created example for S32R274, which shows, how to configure FlexCAN modules and mainly, how to connect transceivers on the NXP EVB for correct communication between modules. Please look at the example and let me know, if it works on your side.

https://community.nxp.com/docs/DOC-333702

If you have any other questions, please feel free to write me back.

Regards,

Martin

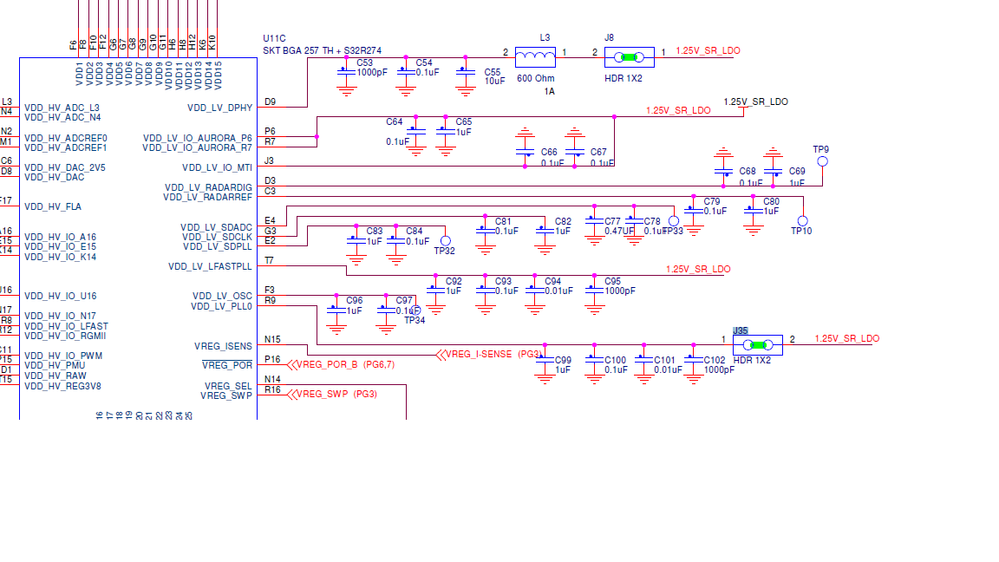

Hi,

in the header description:

It is necessary to remove both J35 jumpers.

Connect J35.2 to PA14 (CAN_1 TX)

Connect J35.4 to PA15 (CAN_1 RX)

CAN0 is connected internally to J37 (this pin is placed on daughter card)

Connect CAN P5.2 to J37.2 (CAN_1 and CAN_0 CANL)

Connect CAN P5.1 to J37.1 (CAN_1 and CAN_0 CANH)

I can't find P5.2 or P5.2 in my schematic.(SPF-28921_D.pdf)

and my J35 is on MCU power connection.

Do I need any other doc?

Hi,

I will summarize the answer to one post:

The Example will be hang at PLL stabilization in Sysclk_Init() on my EVB.

Could you please check, if you use 40MHz crystal? If no, you have to change PLL settings. I see I have incorrect comments in my code. Below is code with correct comments. I tested this code with 40MHz crystal and it works correct.

#define RUN0_MODE 0x4

static void Sysclk_Init(void)

{

CGM.AC3_SC.B.SELCTL =0x01; //connect (40MHz) XTALL to the PLL0 input

/*Set PLL0 to 240MHz with XOSC 40MHz*/

PLLDIG.PLL0DV.R = 0x50024030; //predefined PLL0 divider register

MC_ME.RUN_PC[0].R = 0xFE; /*Enable all modes for all peripherals using

ME_RUN_PC[0]*/

MC_ME.RUN_MC[0].B.XOSCON = 1; //Enable external oscillator

MC_ME.RUN_MC[0].B.PLL0ON = 1; //Enable PLL0 for RUN0 mode

MC_ME.RUN_MC[0].B.SYSCLK = 0x2; //source PLL0 PHI for RUN0 mode

//Mode transition to apply the PLL0 setup and set Normal mode with PLL running

MC_ME.MCTL.R = 0x40005AF0; //RUN0 Mode & Key

MC_ME.MCTL.R = 0x4000A50F; //RUN0 Mode & Key

while(!MC_ME.GS.B.S_PLL0); //ME_GS Wait for PLL stabilization.

while(MC_ME.GS.B.S_MTRANS); //Waiting for end of transaction

/* ME_GS Check RUN0 mode has successfully been entered*/

while(MC_ME.GS.B.S_CURRENT_MODE != RUN0_MODE);

}

In your sample, Why CAN_CLK is set to 60 MHz not 40MHz?

I set CAN Clock to 60MHz, but I do not use this clock. I use 40MHz crystal as a protocol clock instead of CAN clock. It is recommended to use crystal, because it has lower jitter and it is more accurate than CAN clock.

auxiliary clock 7 should be SPT_CLK?

Yes, auxiliary clock 7 is SPT. I took my code from MPC5775K and I did not change the comment.

Regarding you lat post, you have to look at the MPC57xx MOTHERBOARD. I am attaching it to this post.

Regards,

Martin

Hi,

static void InitPeriClkGen(void)

{

...

CGM.AC2_SC.B.SELCTL = 0x2; // Select PLL0 for auxiliary clock 2

CGM.AC2_DC0.B.DIV = 3; // CAN_CLK : Enable aux clk 2 div by 4 ?(60 MHz)

CGM.AC7_SC.B.SELCTL = 0x2; // Select PLL0 for auxiliary clock 7

CGM.AC7_DC0.B.DIV = 1; // CAN_CLK : Enable aux clk 7 div by 2 ?(120 MHz)

...

}

In your sample,

Why CAN_CLK is set to 60 MHz not 40MHz?

auxiliary clock 7 should be SPT_CLK?

Yi-Lin

Hi,

The Example will be hang at PLL stabilization in Sysclk_Init() on my EVB.

I move the GPIO_init setting to my test code.

But it not works.