- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Re: Process ID in SMPU for MPC5745R

Process ID in SMPU for MPC5745R

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Process ID in SMPU for MPC5745R

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

For MPC5745R, from the features file, I see that this SMPU does not support Process ID. Is there a reason for this??

#define FEATURE_SMPU_HAS_PROCESS_IDENTIFIER (0U)

How do I configure regions and which processes can access the region if it is not supported?? There must be some alternative way to use the SMPU?

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

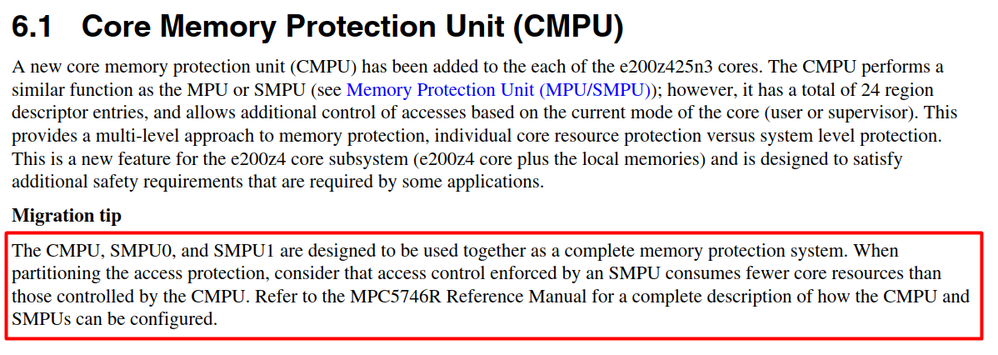

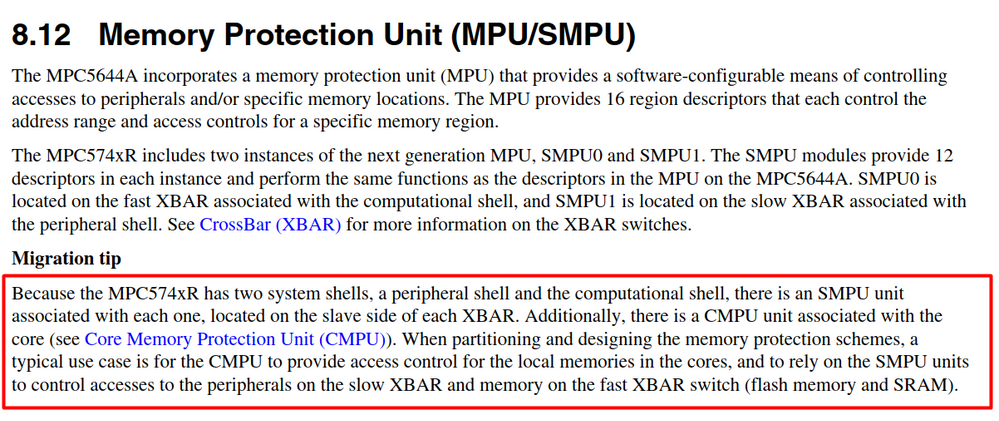

some implementation of SMPU does not have Process ID. It has been removed because it is redundant to CMPU if the core has this sub-unit.

Process ID is either supported by SMPU or CMPU. Specifically MPC5745R has this feature present in CMPU.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

In case of the MPC5745R, there exists an SMPU and a CMPU unit and using the CMPU we can load/monitor the Process ID. This is now my understanding. How can I use the CMPU for managing processes and the SMPU in a collaborative way to manage the regions, then? Rephrasing the question --> How can I use the CMPU and SMPU together to protect memory??

Kind Regards,

Raghu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am attaching screenshots from AN4658, it explains it quite well, I think

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

I was just reading this. Now i understand the concept better. So the CMPU will manage local core related memory and SMPU will control system level memory. Now I am a little confused in protecting memory using CMPU and SMPU in tandem. Let's say, there are 2 software components (SW1 and SW2).I am aware I can save the data related to SW1 can be mapped to either the local d_mem or the m_data in the sram. Let's say I map SW1 data to CMPU, then I can handle the memory protection by defining process IDs for the CMPU of the particular core. But if within SW1, there are functions that access the peripheral, then this data would still be in the SRAM, right? Now if the SW1 is only allowed to write those peripheral registers only during the process ID-x, then how can I manage that??

Basically, I am looking for an example which uses the CMPU and the SMPU in tandem. As far as I am aware, there are no examples or even driver blocks that show the usage of CMPU (individually) and SMPU, together. If you have come across something I can use as a reference, that would be appreciated.

Kind regards,

Raghu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Unfortunately we don't have such example showing both modules together. It is rather application specific.

Following examples exist

Example MPC5744P CMPU Initialization GHS614

Example MPC5748G SMPU initialization GHS614

Example MPC5748G SMPU initialization + Process ID test GHS614

also there is a CMPU configurator here

https://community.nxp.com/docs/DOC-335467

Hope it helps