- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

MPU PID MPC5777C

Hi,

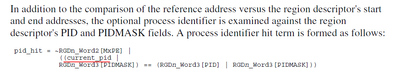

can anyone tell me how the MPU knows which PID every task has? should i set the PID somehow of each task in some special register? because the only thing i found in the reference manual of the MPC5777C is this :

where does the pid_hit get the current pid?

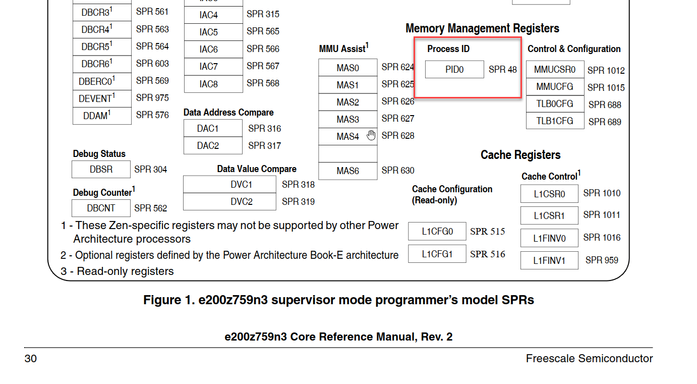

It is given by setting of PID0 core register as on screenshots below:

so if i want to have two tasks each with it's own PID i should so something like this:

void vTaskLed(void *pvParameters)

{

struct TaskLed *apCtx = (struct TaskLed *) pvParameters;

static uint32_t test_read;

for ( ; ; )

{

__asm (

"e_li %r3,0xffff8001\n" // Load the value 0x12345678 into r0

"mtspr 48,%r3\n" // Write the value in r0 to the TBL SPR (SPR number 48)

);

*(uint32_t*)0x4003F000u = 0x1;

gpio_write(apCtx->led, 1);

MSLEEP(TASK_DELAY_1000MS);

gpio_write(apCtx->led, 0);

MSLEEP(TASK_DELAY_1000MS);

}

}

void vTaskLed1(void *pvParameters)

{

struct TaskLed1 *apCtx = (struct TaskLed1 *) pvParameters;

static uint32_t test_read;

for ( ; ; )

{

__asm (

"e_li %r3,0xffff8002\n" // Load the value 0x12345678 into r0

"mtspr 48,%r3\n" // Write the value in r0 to the TBL SPR (SPR number 48)

);

//*(uint32_t*)0x4003F000u = 0x2;

gpio_write(apCtx->led, 1);

MSLEEP(TASK_DELAY_500MS);

gpio_write(apCtx->led, 0);

MSLEEP(TASK_DELAY_500MS);

}

}

Yes, in principle it should be like that.

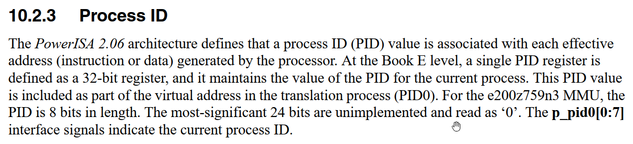

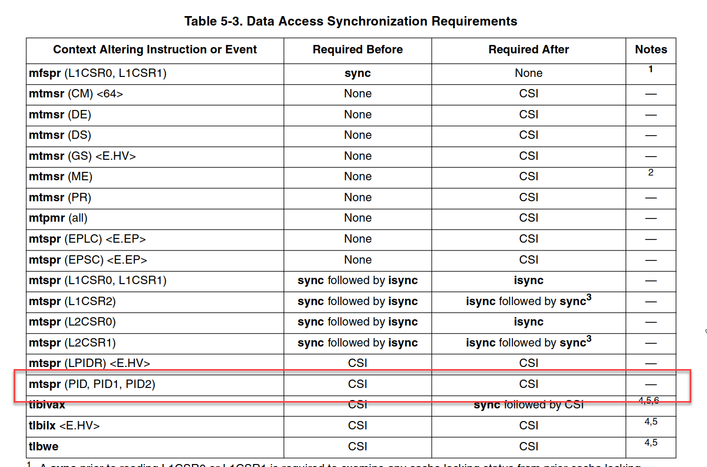

Consider there are also synchronization requirements for accesses to PID registers.

In general way –

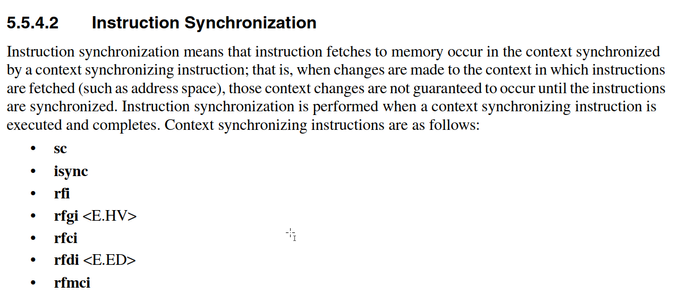

Any instruction that alters the context in which data addresses or instruction addresses are interpreted, or in which instructions are executed, is called a context-altering instruction. A Context Synchronizing Instruction ensures that all changes due to context altering instructions have taken effect.

It is stated either in core RM or EREF RM as well as synchronization requirements for SPRs. EREF RM, section 5.5.4 Synchronization.

Write to PID0 register (spr 48) needs to be followed and predecessed by 'isync', then the solution is bulletproof.