- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Re: MPC5777CEVB External SRAM test example

MPC5777CEVB External SRAM test example

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

We are using MPC5777CEVB and MPC57XXMB.

IDE : s32ds for Power Architecture

OS : Windows 10

Is there any External SRAM test example running on 32ds for Power Architecture?

Regards,

Jinus

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

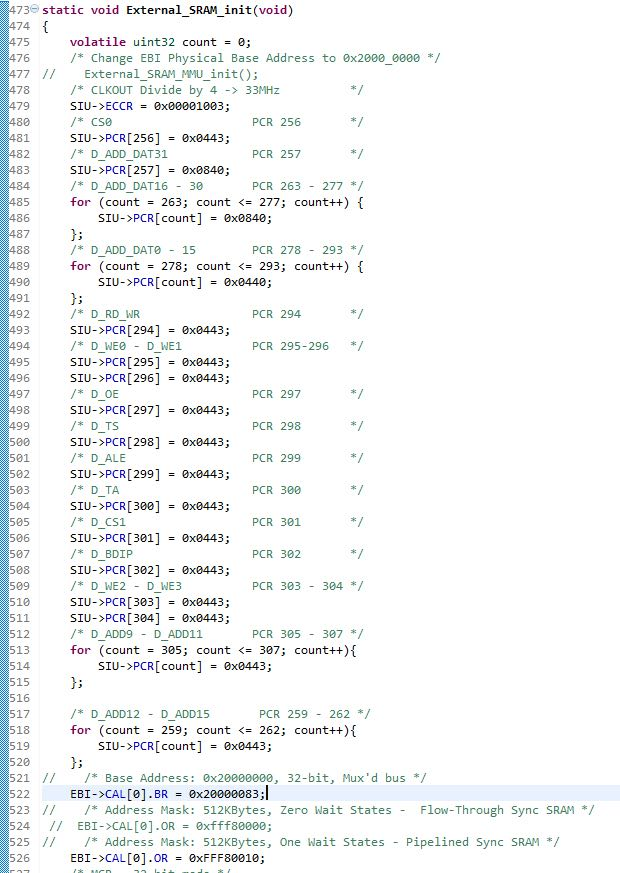

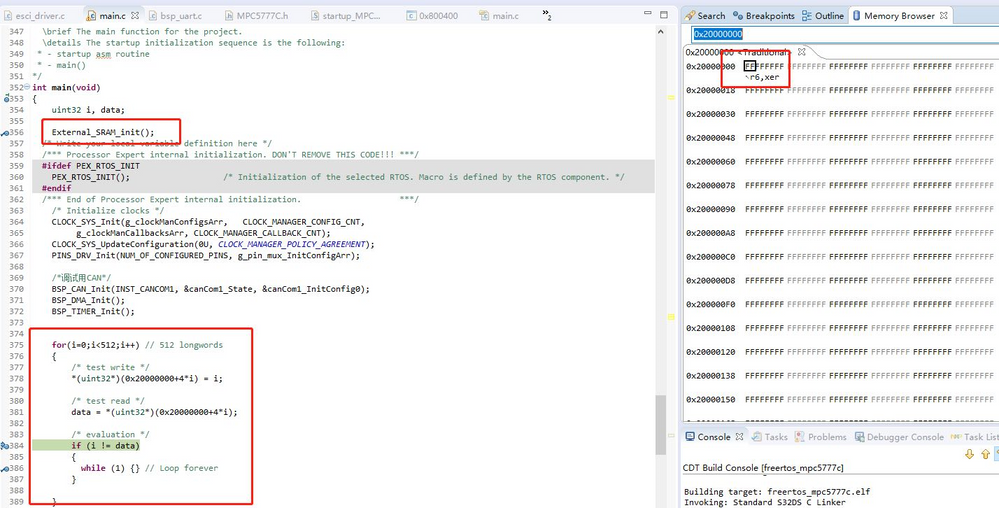

I have just shared example code prepared with Design Studio. it works fine.

You can download it here:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

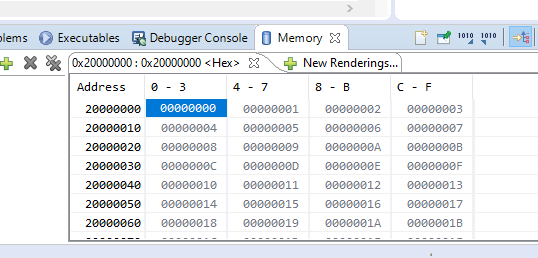

4. Run to check

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

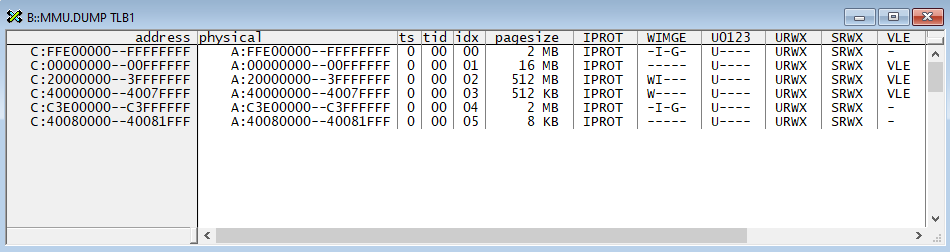

Could you show me MMU table sccrenshot as follows?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

Thanks.

I don't know where i can find this tool. I am sorry.I only have startup_MPC5777C.S file.

MMU configuration shows blow:

#if defined(MMU_CONFIG)

;#****************************** MMU configuration ********************************

#TLB1 = internal flash @ 0x0000_0000, VLE

e_lis r3,0x1001

mtspr 624,r3

e_lis r3,0xC000

e_or2i r3,0x0700

mtspr 625,r3

e_lis r3,0x0000

e_or2i r3,0x0020

mtspr 626,r3

e_lis r3,0x0000

e_or2i r3,0x003F

mtspr 627,r3

msync # Synchronize in case running from flash

tlbwe

se_isync # Synchronize in case running from flash

#TLB3 = internal SRAM @ 0x4000_0000, VLE, Write-Through Cache

e_lis r3,0x1003

mtspr 624,r3

e_lis r3,0xC000

e_or2i 3,0x0480

mtspr 625,r3

e_lis r3,0x4000

e_or2i r3,0x0030

mtspr 626,r3

e_lis r3,0x4000

e_or2i r3,0x003F

mtspr 627,r3

msync # Synchronize in case running from SRAM

tlbwe

se_isync # Synchronize in case running from SRAM

#TLB0 = pbridgeB @ 0xFFE0_0000, Cache inhibited, Guarded

e_lis r3,0x1000

mtspr 624,r3

e_lis r3,0xC000

e_or2i r3,0x0580

mtspr 625,r3

e_lis r3,0xFFE0

e_or2i r3,0x000A

mtspr 626,r3

e_lis r3,0xFFE0

e_or2i r3,0x003F

mtspr 627,r3

tlbwe

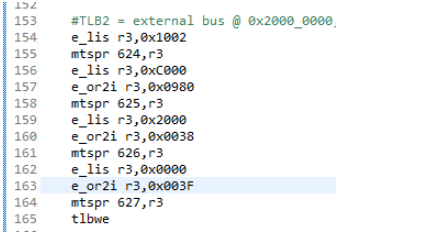

#TLB2 = external bus @ 0x2000_0000, VLE

e_lis r3,0x1002

mtspr 624,r3

e_lis r3,0xC000

e_or2i r3,0x0980

mtspr 625,r3

e_lis r3,0x2000

e_or2i r3,0x0038

mtspr 626,r3

e_lis r3,0x0000

e_or2i r3,0x003F

mtspr 627,r3

tlbwe

#TLB4 = pbridgeA @ 0xC3E0_0000, Cache inhibited, Guarded

e_lis r3,0x1004

mtspr 624,r3

e_lis r3,0xC000

e_or2i r3,0x0580

mtspr 625,r3

e_lis r3,0xC3E0

e_or2i r3,0x000A

mtspr 626,r3

e_lis r3,0xC3E0

e_or2i r3,0x003F

mtspr 627,r3

tlbwe

#TLB5 = 4k stack for each core (will be locked in cache)

# (Note: located just after 512k TLB3 entry for SRAM)

e_lis r3,0x1005

mtspr 624,r3

e_lis r3,0xC000

e_or2i r3,0x0180

mtspr 625,r3

e_lis r3,0x4008

e_or2i r3,0x0000

mtspr 626,r3

e_lis r3,0x4008

e_or2i r3,0x003F

mtspr 627,r3

tlbwe

#endif

Regards,

Jinus

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have just shared example code prepared with Design Studio. it works fine.

You can download it here:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Problem solved. Thanks very much!!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Unfortunately not. But it should not be difficult to port it as the whole setting in located in main.c file.