- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

MPC5748G - verify result of offline BIST

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

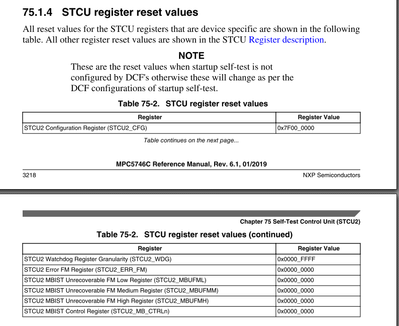

I'm trying to check BIST result on MPC5748G. As far as I understand (from manual) STCU configuration is pre-programmed by NXP to the MPC5748G UTEST flash block. This enables Logic BIST (LBIST) and Memory BIST (MBIST) execution at device startup events. So if BIST is enabled by default I just need to check STCU registers to verify BIST result. State of STCU registers is attached. Captured just before I read STCU registers to check result

All registers have value 0 that indicate LBIST and MBIST are not finished successfully. Maybe not started at all?

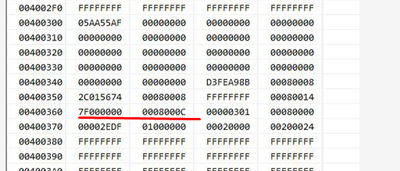

Also UTEST part of memory is captured in the same moment and attached here.

Can you please point me what I'm doing wrong?

Thank you!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

An update.

I was looking closer into manuals of both and the EB820 can be used only as guidance.

As the SPC5748G has different memory partitions and I cant see in SPC5746C any LBIST registers.

I guess this will be a bit hard to program on your own.

I will try to get BIST configuration from application team as soon as possible.

Best regards,

Peter

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

Thank you for help Peter.

We managed to do something. DCF data you provided are programed to the device but it seems that still something is not right. It looks like LBIST 0 is executed successfully but the other two are failed. Is the watchdog reason for that or it's something else? I attached registers capture and the content of the UTEST part of memory.

Can you please take a look on that and try to explain what is happening with BIST now? If you need any other information please let me know.

Thank you!

Best regards,

Tomislav

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

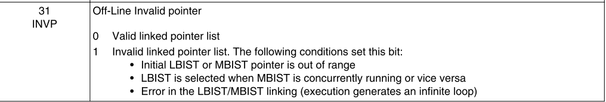

From ERR_STAT I can see that you have invalid pointer error.

Please make sure you have correctly configure BIST pointers and all the following is met.

Your screenshot also show STCU_CFG register with0 content. This is also not correct.

I am not sure when you took those screenshots so Its hard to judge.

Best regards,

Peter

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Peter,

We still not managed to start BIST.

Why we don't have a devices where STCU configuration is pre-programmed by NXP? Do we have devices from some old series or what? We are wasting a lot of time on what was supposed to be trivial and done by the NXP.

Also I found this in manual:

"77.7.7 Definition: Default offline BIST sequence

A default offline built-in self-test (BIST) sequence is an offline BIST sequence whose

configuration NXP has programmed into the chip’s Device Configuration Format (DCF)

records that are stored in the chip’s UTEST flash memory. To determine whether this

chip has a default offline BIST sequence, see the chip-specific STCU2 information.

If this chip has a default offline BIST sequence and you choose to use it, or if it’s the only

one supported by NXP, there is no need to create additional DCF records for the offline

BIST sequence."

Where we can find this chip-specific STCU2 information?

Thank you!

Best regards,

Tomislav

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

As the manual explains:

A default offline built-in self-test (BIST) sequence is an offline BIST sequence whose

configuration NXP has programmed into the chip’s Device Configuration Format (DCF)

records that are stored in the chip’s UTEST flash memory. To determine whether this

chip has a default offline BIST sequence, see the chip-specific STCU2 information.

so if you have default configuration the BIST will run by default after reset phase 1.

From your description your test is not running, so I expect you do not have NXP data in UTEST for BIST.

Where we can find this chip-specific STCU2 information?

77.1 STCU configuration - this is that chapter. But I honestly do not see any info about if you have BIST in chip or not. It just say that there are 2 possibilities.

To determine it simply look at UTEST memory. Pass me here the screenshot of your memory starting at 0x400300 and I can tell you.

We are wasting a lot of time on what was supposed to be trivial and done by the NXP.

I fully understand this, and as I say it is not a simple task. I have already posted for you the factory DCF records which ease the task a lot. But I have no idea what you did with programming and how. Since you didnt share with me your register content nor memory content.

I am curious why you didnt reach out FAE /sales assigned to your company if you struggle so long with it.

On the other hand, I can test the factory DCFs if I find a chip which do not have BIST preprogrammed. Also I will only use NXP Evaluation board, and if you have custom board, you could need to hand-tune the tests.

Let me know what fits best for you,

Best regards,

Peter

Edit: now I see you UTEST in the first post. I can definitely say your sample does not have BIST from NXP factory.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Peter!

Thanks for the fast reply.

I fully understand this, and as I say it is not a simple task. I have already posted for you the factory DCF records which ease the task a lot. But I have no idea what you did with programming and how. Since you didnt share with me your register content nor memory content.

I already sent you content of UTEST memory block and STCU2 registers after we wrote DCF records to the flash. I'm sending all to you again.

Please take a look on that.

I am curious why you didnt reach out FAE /sales assigned to your company if you struggle so long with it.

We will try to flash DCF records again on another board cause the current one is not available anymore. Maybe we did something wrong. We will contact FAE /sales if there is still no progress after that

Thank you!

Best regards,

Tomislav

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Thank you for the fast reply @petervlna

So I need to flash UTEST DCF records to the flash memory? Where I can find the proper configuration (default configuration that was supposed to be stored in memory)? And where exactly need to be stored? At which address? Is there some kind of document that describe this as for mpc5744p (attached)?

Thank you!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

Where I can find the proper configuration (default configuration that was supposed to be stored in memory)?

Not for all versions on chip. As you can see from reference manual note I have posted. Yours has programmed bypass as I can see. I guess all new chips have the BIST pre-programmed. There was AN for programming BIST before.

https://www.nxp.com/docs/en/engineering-bulletin/EB820.pdf

Is there some kind of document that describe this as for mpc5744p (attached)?

This one is written by me. So I do not know if the SPC5748G is as strait as mine. I see only engineering bulletin for SPC5746C ( which is 3MB version of SPC5748G) so it should fit.

But in any case, check if the number of LBIST and MBIST partitions match according to reference manual.

Best regards,

Peter

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

From your screenshot looks that Offline BIST is not programmed on your device by NXP factory.

A default offline built-in self-test (BIST) sequence is an offline BIST sequence whose

configuration NXP has programmed into the chip’s Device Configuration Format (DCF)

records that are stored in the chip’s UTEST flash memory. To determine whether this

chip has a default offline BIST sequence, see the chip-specific STCU2 information.

And this is basically what I see from your screenshot: 7F means null pointer = no BIST execution.

Best regards,

Peter