- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

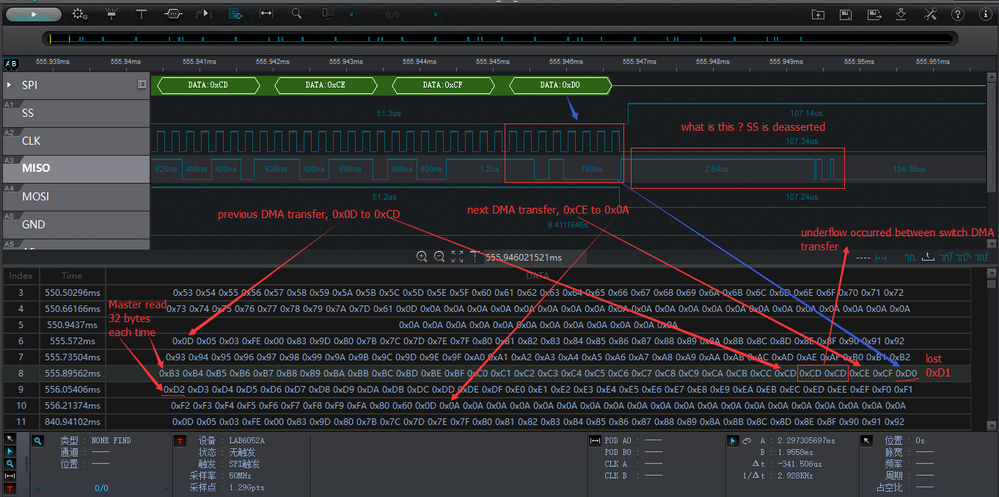

MPC5746C DSPI (slave SPI mode) lost one byte between frames if underflow occurred

Hi, NXP guys

khumphriMandarDeactivated userdhavalRHinnenjimtrudeauMartinvladcentea

In our project, we configure MPC5746C DSPI to work in slave SPI mode,

the Master side clock is 5MHz, read 32byte with continuous chip select asserted.

I found that , it always lost the certain byte between 32-bytes frames if underflow occurred before MPC5746C switch to next DMA transfer (DMA interrupt take time to response and handle).

PS:

1. if I down the Master CLK to 1MHz (no underflow between DMA transfer), this issue disappeared.

2. if the Master side switched the CS to non-continuous mode (deassert CS each byte), still underflow between DMA transfer, but this issue disappeared.

Hi,

if DSPI works as slave, PUSH into TxFIFO must be done in the moment SS is inactive (if you use polling mode).

Let’s have two DSPI's connected as Master-slave. Assume TX-FIFO had 1 entry and a transfer is initiated. When the last-bit is received, the slave's FIFO is empty, hence the internal state-machine moves to an "under-run detect stage" now if we the write the TX-FIFO at this moment the data will not be honored until the slave is de-selected (i.e. SS is de-asserted). If there are subsequent sck clock edges with SS asserted an under-run flag is set although we filled the TX-FIFO even before the next transfer was initiated.

So if TxFIFO is being filled by eDMA according to TFFF flag, TxFIFO will never get into state with 1 entry, so the issue does not happen. Note that XBAR priority for eDMA master must be set for higher value than the core, it is mandatory (just to prevent underflow). If underflow happens, the last byte is repeated as you can see on your screenshots.

Your workarounds are both OK, because both solve the issue I have described above.

hi David,

Thanks for your reply.

but I am using eDMA to fill the slave TxFIFO, and the issue is still happen.

the issue can be reproduce as below:

1. master work at 5MHz, and keep clocking SCK of 32 bytes frame, with continuous CS asserted (CS deasserted between frames).

2. slave(MPC5746C) set the eDMA to transfer 10 bytes to DSPI, then set 25 bytes in eDMA completed ISR.

this is to make sure there is a DSPI underflow occured in one 32 bytes reading frame.

3. the certain byte between 32 bytes frame is always missed.

for example,

MPC5746C first transfer:

01 02 03 04 05 06 07 08 09 0A (10 bytes, in first 32 bytes frame of master)

before eDMA start second transfer, underflow happen:

0A 0A 0A (3 bytes, in first 32 bytes frame of master)

MPC5746C response eDMA completed ISR and start second transfer:

0B 0C 0D ~~~~~~ 1D 1F 20 (19 bytes in first 32 bytes frame of master, CS deasserted, 2 bytes in second 32 bytes frame)

the "1E" is missed, which should be the first byte in second 32 bytes frame.

/WX

Hi, guys

khumphriMandarDeactivated userdhavalRHinnenjimtrudeauMartinvladcenteamarc.paquetteRChapman

any idea ?

/WX