- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Re: MPC5644A - SWT - Software WatchDog Timer

MPC5644A - SWT - Software WatchDog Timer

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all,

I've two questions about SWT settings.

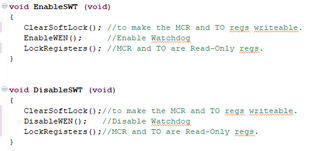

First of all, In referance manual there is a softlock bit which makes the regs are writeable and readable or just readable. I've wanted to try it as shown below.

It works fine like this. However, when the MCR is locked state , I've tried to reach that register (MCR) without removing the lock. It immediately causes the system reset.

Then I realize that there is RIA bit in MCR register. When I read its definition, I understand that when a invalid access happens, the SWT generates just error not system reset (IF MCR_RIA = 0 ).

I've changed RIA as 0, and tried again, but it still resets.

Is there a something that I missed ?

The second question is :

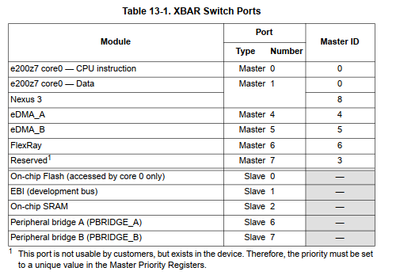

I wanted to lock those registers especially MCR so that it is not accessible even if it's almost unlikely. Because there is MAPn bits which make the master accesses enable/disable. I've seached its meaning in MPC5644A r.m but didn't found. I've found in 5674F r.m

I've disabled the core 0 access by setting MCR_MAP0 = 0 then the whole system is crashed .

Could you explain that why there is a selection like this ? How can I use MCU when I disable the CPU instruction access. Maybe , it is designed as if several core existence but there is one core .

Thank you in advance.

Regards.

HG

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Regarding second question - The description you may find on the first page of XBAR chapter:

It you speak about SWT_MCR[MAPx] fields, then it only affects accesses to SWT. Theoretically it can be handled by DMA for instance, although it does not make to much sense. But mainly, it'll be generic module for multiple devices. Yes, it can be used with devices where masters are mapped differently.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Regarding second question - The description you may find on the first page of XBAR chapter:

It you speak about SWT_MCR[MAPx] fields, then it only affects accesses to SWT. Theoretically it can be handled by DMA for instance, although it does not make to much sense. But mainly, it'll be generic module for multiple devices. Yes, it can be used with devices where masters are mapped differently.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

in the SIU_DIRER register is also option to choose whether IVOR0 or IVOR1 is supposed to be generated and this needs to be unmasked by settting MCR[CE] or MSR[ME].

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I see, you mean an invalid acces to SWT will always cause an interrupt. If SWT bus error occurs, interrupt can be selected as you said.

So, it can be handled in IVOR0 or IVOR1 traps am I right ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It goes into IVOR1 (i.e. bus error) as service sequence is invalid what implies watchdog is not serviced and device is reset by SWT itself subsequently.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Well, it's understood. Thank you Mr @davidtosenovjan .

Do you any thoughts/comments about my second question ?