- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

It seems in the recent cores (especially e200) there are many instructions available in addition to the officially claimed Power ISA 2.03 and the available EREF, VLEPEM, SPEPIM, SPE2PIM, LSPAPURM but there is no overview document listing them all.

I could find mentions of the following APUs/instruction groups in various places:

- e500 branch-locking APU [mentioned in EB622 but could not find the instructions]

- isel instruction(mentioned and described in many places)

- saturation instructions for AutoSAR [mentioned in AN4802 but could not find specific instructions, is this just SPE?]

- Enhanced Reservations APU [?]

- Volatile Context Save/Restore APU [this one is described in EB696]

- Cache Bypass Storage APU [?]

Could be lbcbx, lhcbx, lwcbx, and stwwtx, sthwtx, stbwtx mentioned in MPC5775KRM but no actual descriptions found. - MPU instructions [e200z7260n3 only?]

mpuwe, mpure, mpusync described in MPC5775KRM - EB689 "Additional SPE Instructions" [evfsmadd, ... efsnmsub]

supposedly available only in VLE on e200z3 and e200z6. What about e200z4? - e200z490 (AIOP) custom instructions

some intrinsic functions are described in CWAPPBTR, e.g Byte-Reversing, double/quad word loads and stores, math functions, cache bypass etc. but not the actual instructions. Another list is in AMF-DES-T1052 - SPE 2.1(? I think I've seen it mentioned somewhere but can't find it now. is it EB689?)

Is there an exhaustive list of these (and maybe more) somewhere with descriptions of instructions and opcodes?

已解决! 转到解答。

Hi, I am not sure if I can answer all question, at least trying.

Questions:

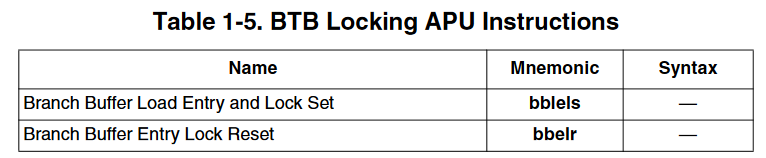

1) e500 branch-locking APU [mentioned in EB622 but could not find the instructions]

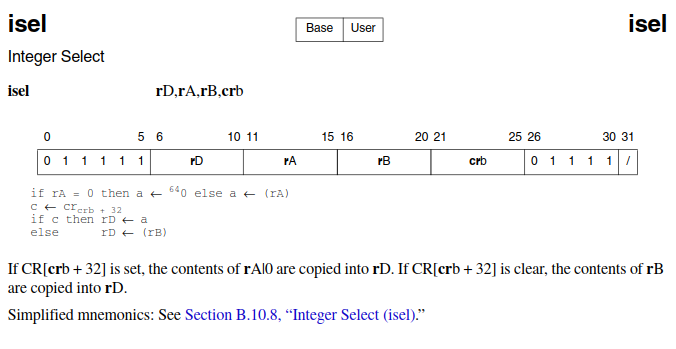

2) isel instruction(mentioned and described in many places)

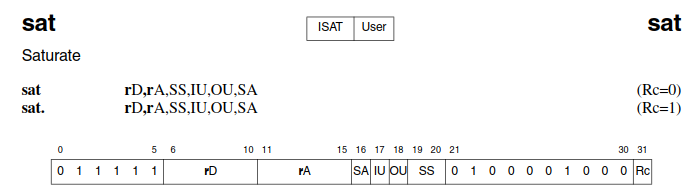

3) saturation instructions for AutoSAR [mentioned in AN4802 but could not find specific instructions, is this just SPE?]

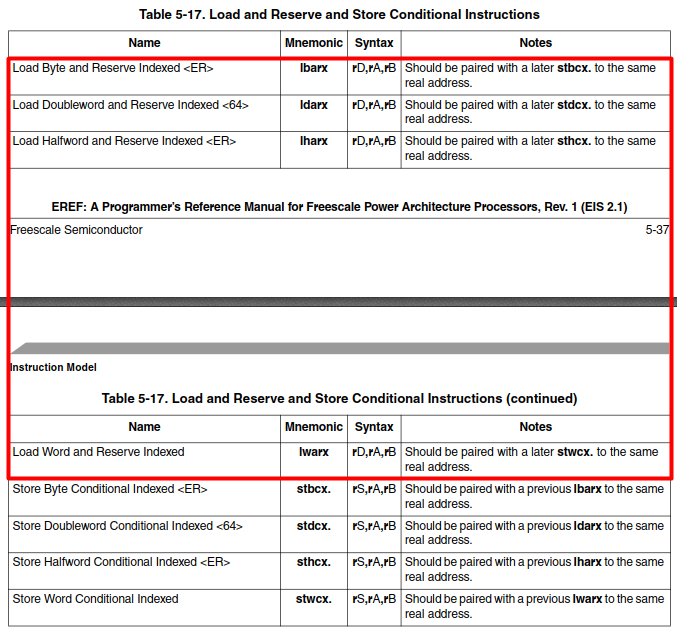

4) Enhanced Reservations APU [?]

5) Volatile Context Save/Restore APU [this one is described in EB696]

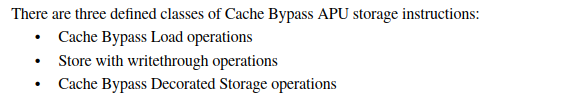

6) Cache Bypass Storage APU [?]

Could be lbcbx, lhcbx, lwcbx, and stwwtx, sthwtx, stbwtx mentioned in MPC5775KRM but no actual descriptions found.

7) MPU instructions [e200z7260n3 only?]

mpuwe, mpure, mpusync described in MPC5775KRM

8) EB689 "Additional SPE Instructions" [evfsmadd, ... efsnmsub]

supposedly available only in VLE on e200z3 and e200z6. What about e200z4?

9) e200z490 (AIOP) custom instructions

some intrinsic functions are described in CWAPPBTR, e.g Byte-Reversing, double/quad word loads and stores, math functions, cache bypass etc. but not the actual instructions. Another list is in AMF-DES-T1052

10) SPE 2.1(? I think I've seen it mentioned somewhere but can't find it now. is it EB689?)

Answers:

1) I have found description in the document below

https://www.nxp.com/docs/en/reference-manual/E500CORERM.pdf

and also in old version of EREF document (EREF 01/2004 Rev. 2). Unfortunately I don't know architecture of all platforms (only e200) so I don't know whether it is used somewhere. Current revision of EREF document does not include the description (EREF_RM Rev. 1 06/2014).

2) You may find it in EREF_RM:

https://www.nxp.com/files-static/32bit/doc/ref_manual/EREF_RM.pdf

3) No, these instructions are described in the EREF_RM manual, it is not SPE instruction set. One example below:

4) These are following 4 instructions, again EREF_RM manual

5) EB696 mentions all these instructions even with opcodes.

6) Yes, these are the isntruction, but there is more in this category:

Unfortunately I haven't found any public description. If you need more info, please create new case and I could possibly send you more info if you have valid NDA (Non-disclosure agreement) with NXP.

7) As I know all devices having CMPU what's all MPC57xx devices excluding MPC5777c and MPC5775B/E according to my knowledge.

8, 10)

SPE2.1 specification is not publicly available, see answer no.6.

Hi, I am not sure if I can answer all question, at least trying.

Questions:

1) e500 branch-locking APU [mentioned in EB622 but could not find the instructions]

2) isel instruction(mentioned and described in many places)

3) saturation instructions for AutoSAR [mentioned in AN4802 but could not find specific instructions, is this just SPE?]

4) Enhanced Reservations APU [?]

5) Volatile Context Save/Restore APU [this one is described in EB696]

6) Cache Bypass Storage APU [?]

Could be lbcbx, lhcbx, lwcbx, and stwwtx, sthwtx, stbwtx mentioned in MPC5775KRM but no actual descriptions found.

7) MPU instructions [e200z7260n3 only?]

mpuwe, mpure, mpusync described in MPC5775KRM

8) EB689 "Additional SPE Instructions" [evfsmadd, ... efsnmsub]

supposedly available only in VLE on e200z3 and e200z6. What about e200z4?

9) e200z490 (AIOP) custom instructions

some intrinsic functions are described in CWAPPBTR, e.g Byte-Reversing, double/quad word loads and stores, math functions, cache bypass etc. but not the actual instructions. Another list is in AMF-DES-T1052

10) SPE 2.1(? I think I've seen it mentioned somewhere but can't find it now. is it EB689?)

Answers:

1) I have found description in the document below

https://www.nxp.com/docs/en/reference-manual/E500CORERM.pdf

and also in old version of EREF document (EREF 01/2004 Rev. 2). Unfortunately I don't know architecture of all platforms (only e200) so I don't know whether it is used somewhere. Current revision of EREF document does not include the description (EREF_RM Rev. 1 06/2014).

2) You may find it in EREF_RM:

https://www.nxp.com/files-static/32bit/doc/ref_manual/EREF_RM.pdf

3) No, these instructions are described in the EREF_RM manual, it is not SPE instruction set. One example below:

4) These are following 4 instructions, again EREF_RM manual

5) EB696 mentions all these instructions even with opcodes.

6) Yes, these are the isntruction, but there is more in this category:

Unfortunately I haven't found any public description. If you need more info, please create new case and I could possibly send you more info if you have valid NDA (Non-disclosure agreement) with NXP.

7) As I know all devices having CMPU what's all MPC57xx devices excluding MPC5777c and MPC5775B/E according to my knowledge.

8, 10)

SPE2.1 specification is not publicly available, see answer no.6.

Thanks David, this is very helpful!

By the way, I found where I saw SPE 2.1 mentioned. It was in AN4802:

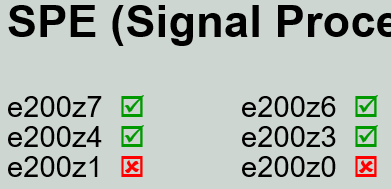

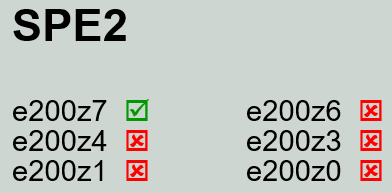

The Signal Processing Engine (SPE) Auxiliary Processing Unit

supports a full range of instructions for digital signal processing

algorithms. There are currently two major versions of the SPE (1.1 and

2.1) that are supported on the MPC57xx devices.

Can you at least tell me what was added in 2.1? Any new instructions? Also, what's the difference between the original SPE and 1.1? Thanks.

The only 'comparison' I have found in the following presentation

e200 Core Training relevant to MPC55xx and MPC56xx device family

telling that SPE2

I don't know any descriptive document other than:

https://www.nxp.com/docs/en/reference-manual/SPEPIM.pdf

https://www.nxp.com/docs/en/reference-manual/SPE2PIM.pdf

These however does not contain opcodes (SPE2PEM manual does not exist).