- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

We use MPC5746R and FS6500 as our basic hardware combination. We try to config the FCCU EOUT mode to Bi-Stable since its the only way FS6500 recognise.

The thing is we config the EOUT0 and EOUT1 to GPIO mode, we can control these two pin state.

But we can't control the EOUT1(not EOUT0) with error output mode.

Even by setting FOM to the TEST1 mode to driver both EOUT pin to high level, EOUT1 is still low.

We refer to the example https://community.nxp.com/docs/DOC-341616 MPC5746R FCCU Alarm State.

Still no luck.

We run out of options right now, so we need help to understand how to improve our code to achieve a right FCCU output curve.

Thanks.

已解决! 转到解答。

Well, what to say.

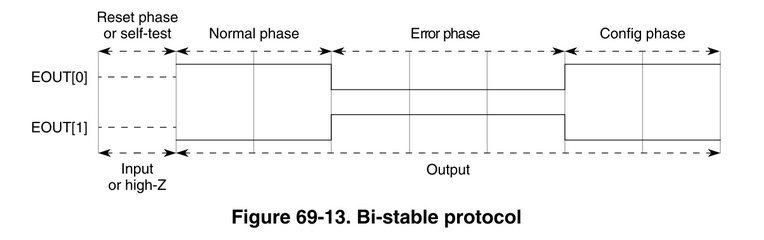

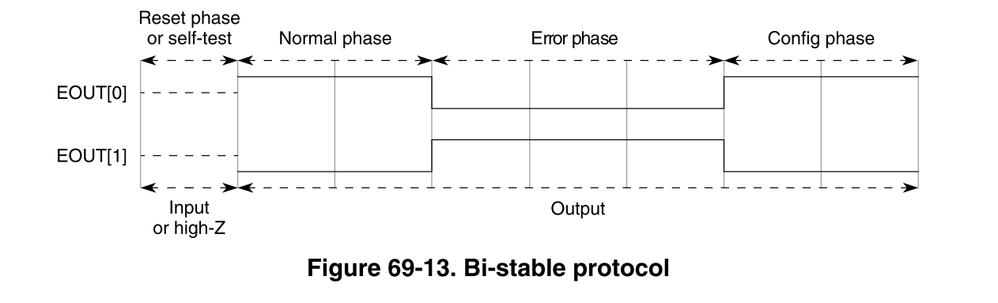

You now must know how the bi-stable protocol works (I have posted it twice).

Ill do it one last time:

Looks like document of SBC chip is wrong and guys who wrote the document have no clue about FCCU safety protocols :smileyhappy: if they recommend this.

For some microcontrollers we have fixed multiplexer on FCCU EOUT pins so they always reflect bi-stable (reset) levels and there are no need of pull resistors. But this part for not designed for pure safety purpose like for example (MPS5744P), so you have to add (correctly) pull resistors.

Peter

Hi,

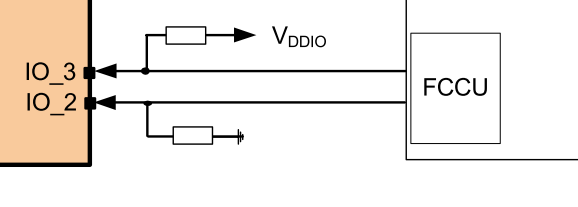

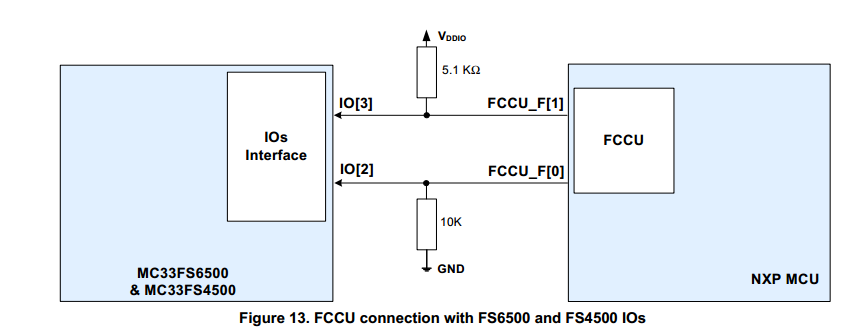

This is described in FS6500 ref manual:

Connect the pull up and pull down resistors to match bi-stable protocol when the micro FCCU EOUT pins are in high-z state.

IO_3 pull up to EOUT0

IO_2 pull down to EOUT1

Peter

Hi, peter,

I already have these two resistors, but still I can't control the EOUT1 pin.

So I config the two EOUT pins to idle pins not connected to the FS6500, use the test2 mode to control the EOUT pins.

The result is still EOUT1 out of control, but no the EOUT0.

Hi,

To control EOUT pin you have 2 possibilities.

1. install pull resistors

2. configure SIUL unit

during and after reset EOUT pins are in high-Z state until they are configured in SIUL module. This is behaving for SBC chip as fault state.

So if you install pull resistors in EOUT you must see during reset a high and low level on those pins corresponding to Normal state of FCCU.

This mean EOUT0 --> pull up and EOUT1 --> pull down.

Just measure EOUT with scope or multimeter to see if during reset and before SIUL configuration EOUT pins has correct voltage level.

You dont need any SW in micro either to do this test.

Peter

Hi, peter

I fount something inconsistent.

Here is some screen shot I took from safety manual for FS6500 and FS4500.

From this pic, FCCU_F0 connect to the IO[2], FCCU_F1 connect to the IO[3].

So, instead of a normal reset level, we have a error reset level. I wonder if this is the reason I have a problem controlling the FCCU EOUT.

Does this mean this document is wrong?

Well, what to say.

You now must know how the bi-stable protocol works (I have posted it twice).

Ill do it one last time:

Looks like document of SBC chip is wrong and guys who wrote the document have no clue about FCCU safety protocols :smileyhappy: if they recommend this.

For some microcontrollers we have fixed multiplexer on FCCU EOUT pins so they always reflect bi-stable (reset) levels and there are no need of pull resistors. But this part for not designed for pure safety purpose like for example (MPS5744P), so you have to add (correctly) pull resistors.

Peter

Hi,peter

I need your help with some more questions.

Before I said I can't control EOUT1 but not EOUT0, at that time, I use PI0 and PI1 as FCCU output pin.

Even though I adjust the pull resistors, the outputs don't change.

So I change the FCCU output pins to PJ0 and PJ1. This time I can't control EOUT0 but not EOUT1.

Then I config all these four pins, PI1 and PJ1 can have the right output not the PI0 and PJ0.

According to the IO_Signal_Description_and_Input_Multiplexing_Tables, there are seven FCCU output pins.

I wonder is there some other config rules that only certain FCCU output pins can work together, I can't find any information regarding this. But the experiment outcome suggest there is some connection.

So I wonder if you know something about this. ( I hope I have described my experiments clearly)

Thanks.