- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

ECSM - Writing ECR Register Problem

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

MCU = MPC5674F

IDE = CodeWarrior 10.6

Hi,

I want to use ECSM module in order to report the correctable and non-correctable bit errors. I am having a problem about setting the ECSM_ECR Register bits. I am writing 1 (one) into the bits, however they are remaining as 0 (zero). I could not figure out why it happens.

Here how I am setting the bits to enable reporting the errors.

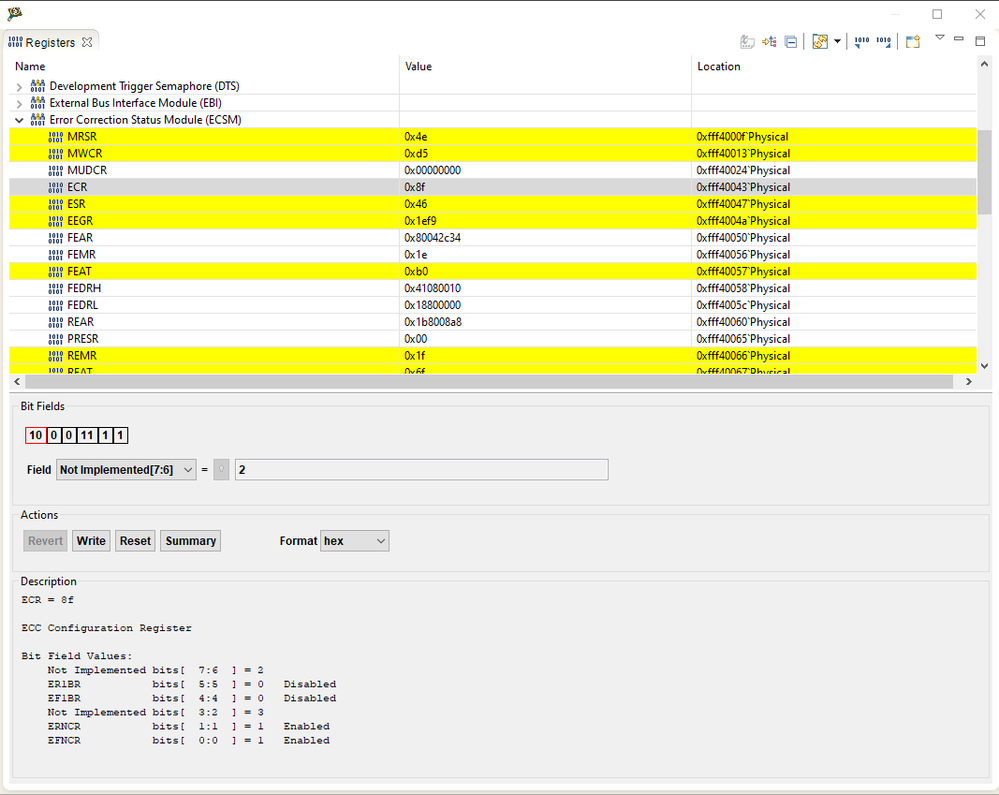

When it stops at the breakpoint, I checked the Register Window of the CodeWarrior 10.6 which is shown in the below. As you can see, the ECR register bits are not set.

Note: I remove breakpoints and tried to run, again ECR register bits are not set. Also, I tried to write 1 to bits by using the Register Window, however still the value of the bits are remain as 0.

Do you have any idea or information about it?

Thanks,

Mert

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi everyone, it's me again

Unfortunately, I couldn't achieve to control ECSM module. If there is an idea to give me, I'd appreciate for it.

Best regards,

Mert.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi all , I've used PPC-PROGNEXSUS to erase the chip and then program. Unfortunately it didn't work, I couldn't write on ECR register as well.

Could someone share a screenshot that shows it's really possible to use ECSM module ? I'm losing my religion

Edit : @ErichStyger

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi everyone,

In case of I miss something on initialization of ECSM, can you tell me how I initiliaze the ECSM? I mean, is there any sequence that I must control before and after initializing the ECSM?

Best regards,

Mert.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

I have gone trough your post and so far everything look correct.

Always check the physical memory itself instead of any debugger window view, which can point to different address in memory in case of such issues.

Did you try directly in physical memory at 0xFFF40043 change the value via debugger? This must work.

Try it on erased micro, in case some register protection mechanism is blocking your access.

Best regards,

Peter

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @petervlna ,

Thanks for your answer.

Always check the physical memory itself instead of any debugger window view, which can point to different address in memory in case of such issues.

I checked the physical memory via Memory window of the CW for MCU during all debugs.

Did you try directly in physical memory at 0xFFF40043 change the value via debugger? This must work.

I tried to change the ECSM_ECR values from the Registers Window via PE micro debugger. It didn't work for ECSM_ECR. However, I am able to write to ETPU module and PCR registers via same PE micro debugger.

Try it on erased micro, in case some register protection mechanism is blocking your access.

I assumed that, my other codes in the project may be the cause of the writing problem to ECSM. Therefore, I created a new Bareboard project for MPC5674F and I just wanted to enable RAM and FLASH reporting of ECSM.

Here how I create the new project in CW for MCU v10.6;

- File -> New -> Bareboard Project

- I entered a project name, then click the next button

- I selected the Qorivva -> MPC56xxF Family -> MPC5674F and I selected the "Application" as a Project Type/Output. Then click the Next button.

- I selected the "P&E USB-ML-PPCNEXUS" as Connection type to be used.

- I selected the "C" as langueage, "Use the BookE instruction set" as Instruction Set Options and "SPFP_Only" as Floating Point.

Here what I added to created empty MPC5674F bareboard project;

#include "MPC5674F.h"

int main(void) {

volatile int i = 0;

/* physical address of the ECSM_ECR register */

unsigned int* addr_ECSM_ECR = (unsigned int*) 0xfff40043; // I added

/* writing the physical adress of the ECSM_ECR register directly */

*addr_ECSM_ECR = 0x33; // I added

/* Also I run the below one. */

ECSM.ECR.R = 0x33; // I added

/* Loop forever */

for (;;) {

i++;

}

}

When I built and debugged the project in the RAM, I couldn't see any changes in physical address of ECSM_ECR register in Memory window and Register window.

When I built and debugged the project in the FLASH, at the part of the writing the physical address of the ECSM_ECR register (when I try to step into at the stw r0, 0(r31)), the code flow goes into IVOR1trap (Machine check).

Here the code and assembly language of it;

Here, what I came after stepping into the "stw r0, 0(r31)";

Code flow stucking at the IVOR1trap.

I did run at MPC5674F MCU and CodeWarrior for MCU v10.6.

I’d appreciate it if anyone could;

- create a bareboard project for one of the MPC5674F, MPC5644A or MPC5642A by using the above five steps that I described

- change the main.c with my main code that is above

- build and debug the project

- and see the ECSM_ECR register is wrote with 0x33 (and it must maintain the valuei in run-time)

- lastly share the result in this post

@petervlna I really appreciate your helps.

I look forward to your results and anwers.

Best regards,

Mert.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi all, has there been any progress on this topic ?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @petervlna and @davidtosenovjan, do you have any idea?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi everyone, I still could not solve the problem. Please save me from this. Smile smile xD

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @petervlna and @davidtosenovjan, do you have any idea about the problems?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

MCU = MPC5674F

IDE = CodeWarrior for MCU v10.6

Hi Peter,

I tried the writing whole register at once, unfortunetly it did not work.

Here is the address definition of the ECSM module in header file.

#define ECSM (*( volatile struct ECSM_tag *) 0xFFF40000)

The offset of the ECR Register is 0x0043. Therefore the physical address of the ECSM_ECR register is 0xFFF40043.

The related ECSM part in the header file is below.

/****************************************************************************/

/* MODULE : ECSM */

/****************************************************************************/

struct ECSM_tag {

union { /* Processor core type */

vuint16_t R;

} PCT;

union { /* Platform revision */

vuint16_t R;

} REV;

uint32_t ECSM_reserved0004; /* 0x0004-0x0007 */

union { /* IPS Module Configuration */

vuint32_t R;

} IMC;

uint8_t ECSM_reserved000C[3]; /* 0x000C-0x000E */

union { /* Miscellaneous Reset Status Register */

vuint8_t R;

struct {

vuint8_t POR:1;

vuint8_t DIR:1;

vuint8_t SWTR:1;

vuint8_t:5;

} B;

} MRSR;

uint8_t ECSM_reserved0010[51]; /* 0x0010-0x0042 */

union { /* ECC Configuration Register */

vuint8_t R;

struct {

vuint8_t:2;

vuint8_t ER1BR:1;

vuint8_t EF1BR:1;

vuint8_t:2;

vuint8_t ERNCR:1;

vuint8_t EFNCR:1;

} B;

} ECR;

uint8_t ECSM_reserved0044[3]; /* 0x0044-0x0046 */

union { /* ECC Status Register */

vuint8_t R;

struct {

vuint8_t:2;

vuint8_t R1BC:1;

vuint8_t F1BC:1;

vuint8_t:2;

vuint8_t RNCE:1;

vuint8_t FNCE:1;

} B;

} ESR;

uint16_t ECSM_reserved0048; /* 0x0048-0x0049 */

union { /* ECC Error Generation Register */

vuint16_t R;

struct {

vuint16_t:2;

vuint16_t FRC1BI:1;

vuint16_t FR11BI:1;

vuint16_t:2;

vuint16_t FRCNCI:1;

vuint16_t FR1NCI:1;

vuint16_t:1;

vuint16_t ERRBIT:7;

} B;

} EEGR;

uint32_t ECSM_reserved004C; /* 0x004C-0x004F */

union { /* Flash ECC Address Register */

vuint32_t R;

struct {

vuint32_t FEAR:32;

} B;

} FEAR;

uint16_t ECSM_reserved0054; /* 0x0054-0x0055 */

union { /* Flash ECC Master Number Register */

vuint8_t R;

struct {

vuint8_t:4;

vuint8_t FEMR:4;

} B;

} FEMR;

union { /* Flash ECC Attributes Register */

vuint8_t R;

struct {

vuint8_t WRITE:1;

vuint8_t SIZE:3;

vuint8_t PROT0:1;

vuint8_t PROT1:1;

vuint8_t PROT2:1;

vuint8_t PROT3:1;

} B;

} FEAT;

union { /* Flash ECC Data Register High */

vuint32_t R;

struct {

vuint32_t FEDH:32;

} B;

} FEDRH;

union { /* Flash ECC Data Register Low */

vuint32_t R;

struct {

vuint32_t FEDL:32;

} B;

} FEDRL;

union { /* RAM ECC Address Register */

vuint32_t R;

struct {

vuint32_t REAR:32;

} B;

} REAR;

uint8_t ECSM_reserved0064; /* 0x0064 */

union { /* RAM ECC Syndrome Register */

vuint8_t R;

struct {

vuint8_t RESR:8;

} B;

} RESR;

union { /* RAM ECC Master Number Register */

vuint8_t R;

struct {

vuint8_t:4;

vuint8_t REMR:4;

} B;

} REMR;

union { /* RAM ECC Attributes Register */

vuint8_t R;

struct {

vuint8_t WRITE:1;

vuint8_t SIZE:3;

vuint8_t PROT0:1;

vuint8_t PROT1:1;

vuint8_t PROT2:1;

vuint8_t PROT3:1;

} B;

} REAT;

union { /* RAM ECC Data Register */

vuint32_t R;

struct {

vuint32_t REDH:32;

} B;

} REDRH;

union { /* RAM ECC Data Register */

vuint32_t R;

struct {

vuint32_t REDL:32;

} B;

} REDRL;

uint32_t ECSM_reserved0070[4068]; /* 0x0070-0x3FFF */

};

Here is the function that I used to enable ECC reporting.

void enableECCReporting(void)

{

// Enable Flash 1-bit Reporting

ECSM.ECR.B.EF1BR = 1u;

// Enable Flash Non-Correctable Reporting

ECSM.ECR.B.EFNCR = 1u;

// Enable RAM 1-bit Reporting

ECSM.ECR.B.ER1BR = 1u;

// Enable RAM Non-Correctable Reporting

ECSM.ECR.B.ERNCR = 1u;

}

Also here is the assembly code of the enableECCReporting function. I checked the r0 and r3 values for every stb r0, 67(r3) assembly code and write the values of the r0 and r3 register into the figure.

Until this point, everything looks fine right? However, either memory location of the ECSM_ECR in Memory Window and the ECR register representation in the Variables Window are not changed. Here is the values shown in the Memory Window and Variables Windows for ECR register.

-----------------------------------------------------------------------------------------------------------------------------------------------------

Here also the code when I used to write whole register at once.

void enableECCReporting(void)

{

// Enable Flash 1-bit Reporting

// Enable Flash Non-Correctable Reporting

// Enable RAM 1-bit Reporting

// Enable RAM Non-Correctable Reporting

ECSM.ECR.R = 0x33;

}

The assemly code of the upper code block.

As I state the top of this message, it is not work.

Extra Observation:

The value of any ECSM module registers are not changing in run-time at MPC5674F. I run the code without breakpoints and monitored the values in the Register Window for ECSM. However, I couldn't see any changes in the registers.

*************************************************************************************************************

MCU = MPC5644A

IDE = CodeWarrior for MCU v10.6

Also, I wanted to check the ECSM module at MPC5644A. I have the nearly same ECSM code for the MPC5644A MCU.

In MPC5644A, the values of the ECR register change strangely. For example, the values of the Unimplenmented part of the ECR register takes value as 1. However, I am not setting them. Also, ER1BR, EF1BR, ERNCR and EFNCR bits takes values 0 and 1 randomly. I am doing anything to change them. Unfortunetly this is not just for ECR register of the ECSM. All ECSM register taking randomly value. However, there is code to do that. It is too strange.

Here is the address definition of the ECSM module in MPC5644A header file.

#define ECSM (*( volatile struct ECSM_tag *) 0xFFF40000)

The related ECSM part in MPC5644A header file is below.

/****************************************************************************/

/* MODULE : ECSM */

/****************************************************************************/

struct ECSM_tag {

union { /* Processor core type */

vuint16_t R;

} PCT;

union { /* Platform revision */

vuint16_t R;

} REV;

union { /* AXBS Master Configuration */

vuint16_t R;

} AMC;

union { /* AXBS Slave Configuration */

vuint16_t R;

} ASC;

union { /* IPS Module Configuration */

vuint32_t R;

} IMC;

uint8_t ECSM_reserved000C[3]; /* 0x000C-0x000E */

union { /* Miscellaneous Reset Status Register */

vuint8_t R;

struct {

vuint8_t POR:1;

vuint8_t DIR:1;

vuint8_t:6;

} B;

} MRSR;

uint8_t ECSM_reserved0010[3]; /* 0x0010-0x0012 */

union { /* Miscellaneous Wakeup Control */

vuint8_t R;

struct {

vuint8_t ENBWCR:1;

vuint8_t:3;

vuint8_t PRILVL:4;

} B;

} MWCR;

uint32_t ecsm_reserved0014[4]; /* 0x0014 - 0x0023 */

union { /* Miscellaneous User Defined Control */

vuint32_t R;

struct {

vuint32_t:1;

vuint32_t SWSC:1;

vuint32_t:30;

} B;

} MUDCR;

uint32_t ecsm_reserved0028[6]; /* 0x0028 - 0x003C*/

uint8_t ecsm_reserved0040[3]; /* 0x0040 - 0x0042*/

union {

vuint8_t R;

struct {

vuint8_t:2;

vuint8_t ER1BR:1;

vuint8_t EF1BR:1;

vuint8_t:2;

vuint8_t ERNCR:1;

vuint8_t EFNCR:1;

} B;

} ECR; /* ECC Configuration Register @baseaddress + 0x43 */

uint8_t ecsm_reserved0044[3]; /* 0x0044 - 0x0046*/

union {

vuint8_t R;

struct {

vuint8_t:2;

vuint8_t R1BC:1;

vuint8_t F1BC:1;

vuint8_t:2;

vuint8_t RNCE:1;

vuint8_t FNCE:1;

} B;

} ESR; /* ECC Status Register @baseaddress + 0x47 */

uint8_t ecsm_reserved0048[2]; /* 0x0048 - 0x0049*/

union {

vuint16_t R;

struct {

vuint16_t FRCAP:1;

vuint16_t:1;

vuint16_t FRC1BI:1;

vuint16_t FR11BI:1;

vuint16_t:2;

vuint16_t FRCNCI:1;

vuint16_t FR1NCI:1;

vuint16_t:1;

vuint16_t ERRBIT:7;

} B;

} EEGR; /* ECC Error Generation Register @baseaddress + 0x4A */

uint32_t ecsm_reserved004C; /* 0x004C - 0x004F*/

union {

vuint32_t R;

struct {

vuint32_t FEAR:32;

} B;

} FEAR; /* Flash ECC Address Register @baseaddress + 0x50 */

uint16_t ecsm_reserved0054; /* 0x0054 - 0x0055*/

union {

vuint8_t R;

struct {

vuint8_t:4;

vuint8_t FEMR:4;

} B;

} FEMR; /* Flash ECC Master Register @baseaddress + 0x56 */

union {

vuint8_t R;

struct {

vuint8_t WRITE:1;

vuint8_t SIZE:3;

vuint8_t PROT0:1;

vuint8_t PROT1:1;

vuint8_t PROT2:1;

vuint8_t PROT3:1;

} B;

} FEAT; /* Flash ECC Attributes Register @baseaddress + 0x57 */

union {

vuint32_t R;

struct {

vuint32_t FEDH:32;

} B;

} FEDRH; /* Flash ECC Data High Register @baseaddress + 0x58 */

union {

vuint32_t R;

struct {

vuint32_t FEDL:32;

} B;

} FEDRL; /* Flash ECC Data Low Register @baseaddress + 0x5C */

union {

vuint32_t R;

struct {

vuint32_t REAR:32;

} B;

} REAR; /* RAM ECC Address @baseaddress + 0x60 */

uint8_t ecsm_reserved0064; /* 0x0064 - 0x0065*/

union {

vuint8_t R;

struct {

vuint8_t PRESR:8;

} B;

} PRESR; /* RAM ECC Syndrome @baseaddress + 0x65 */

union {

vuint8_t R;

struct {

vuint8_t:4;

vuint8_t REMR:4;

} B;

} REMR; /* RAM ECC Master @baseaddress + 0x66 */

union {

vuint8_t R;

struct {

vuint8_t WRITE:1;

vuint8_t SIZE:3;

vuint8_t PROT0:1;

vuint8_t PROT1:1;

vuint8_t PROT2:1;

vuint8_t PROT3:1;

} B;

} REAT; /* RAM ECC Attributes Register @baseaddress + 0x67 */

union {

vuint32_t R;

struct {

vuint32_t REDH:32;

} B;

} REDRH; /* RAM ECC Data High Register @baseaddress + 0x68 */

union {

vuint32_t R;

struct {

vuint32_t REDL:32;

} B;

} REDRL; /* RAMECC Data Low Register @baseaddress + 0x6C */

};

Here is the function that I used to enable ECC reporting.

void initializeECSM(void)

{

// Enable Flash 1-bit Reporting

ECSM.ECR.B.EF1BR = 1;

// Enable Flash Non-Correctable Reporting

ECSM.ECR.B.EFNCR = 1;

// Enable RAM 1-bit Reporting

ECSM.ECR.B.ER1BR = 1;

// Enable RAM Non-Correctable Reporting

ECSM.ECR.B.ERNCR = 1;

}

Here is the weird values of ECSM registers in the Register Window.

Also the value in the related physical addresses seen in Memory Window and Register Window are not same!

Assembly code for initializeECSM function in MPC5644A and MPC5674F are same and the r0 and r3 values are same.

CAN YOU HELP ME?

Best regards,

Mert.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

The function looks fine to me, however i cant be sure as I do not have your header file.

Either share also address definition of this register in header file, or assembly code.

What you can do is to write whole register at once, not via byte access.

And you can also simply assembly debug the function and see if the core is writing to ECR register and where is the issue.

Best regards,

Peter