- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- BUS MASTER Mapping with MPU_RGD0_WORD2/MPU_RGDAACn

BUS MASTER Mapping with MPU_RGD0_WORD2/MPU_RGDAACn

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

BUS MASTER Mapping with MPU_RGD0_WORD2/MPU_RGDAACn

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

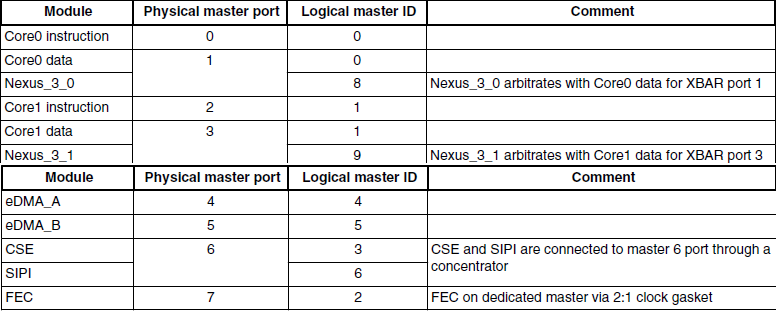

As in MPC5777C, there are 8 Bus master, which are given in below table, if i am not wrong:

(Original Table at 9-1 in ref. mannual)

So,

CASE1:

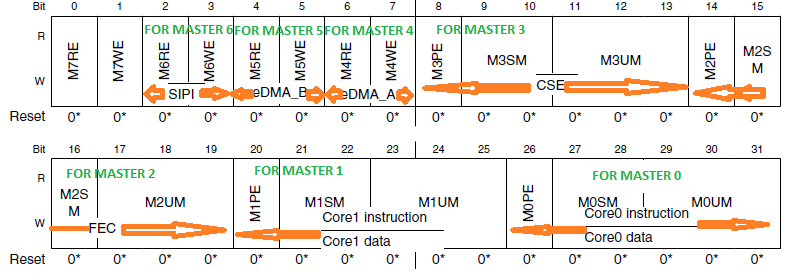

1. Suppose Core0, is running and want to provide access permission :

Is to achieve the above point 1 we need to configure M1UM,M1SM,M1PE bits in MPU_RGD0_WORD2/MPU_RGDAACn?

2. If Core1 is running and i want to provide access permission :

Is to achieve the above point 2 we need to configure M3UM,M3SM,M3PE bits in MPU_RGD0_WORD2/MPU_RGDAACn?

and thus similar way for Bus master

4(eDMA_A), we need to configure bits M4RE,M4WE

5(eDMA_B), we need to configure bits M5RE,M5WE

6(CSE/SIPI) we need to configure bits M6RE,M6WE and

for 7(FEC) we need to configure bits M7RE,M7WE

OR

CASE2:

Like Below, what i have try to figure out, please let me know, if i am TRUE-

Is above register should mapped according to Physical master port OR Logical master ID?

Please help me..

Thank You!