- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- MPC5xxx Knowledge Base

- :

- Example MPC5777C-eTPU_GPIO_test GHS714

Example MPC5777C-eTPU_GPIO_test GHS714

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report Inappropriate Content

Example MPC5777C-eTPU_GPIO_test GHS714

Example MPC5777C-eTPU_GPIO_test GHS714

********************************************************************************

* Detailed Description:

* A simple example configures eTPU engine B channels 0/1 for GPO/GPI. It is

* needed to connect these pins by wire. Output wave is generated by eTPU GPIO

* output function and inputs are read by fs_etpu_gpio_input_immed function

* latching just current pin state. Pin history is displayed in ISR.

*

* Note: It is needed to configure IGF module, otherwise inputs does not pass

* to eTPU module.

*

* ------------------------------------------------------------------------------

* Test HW: MPC5777C-512DS Rev.A + MPC57xx MOTHER BOARD Rev.C

* MCU: PPC5777CMM03 2N45H CTZZS1521A

* Fsys: PLL1 = core_clk = 264MHz, PLL0 = 192MHz

* Debugger: Lauterbach Trace32

* Target: internal_FLASH

* Terminal: 19200-8-no parity-1 stop bit-no flow control on eSCI_A

* EVB connection: ETPUB0 (PortR P25-1) --> ETPUB1 (PortR P25-0) by wire

*

********************************************************************************

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hello David,

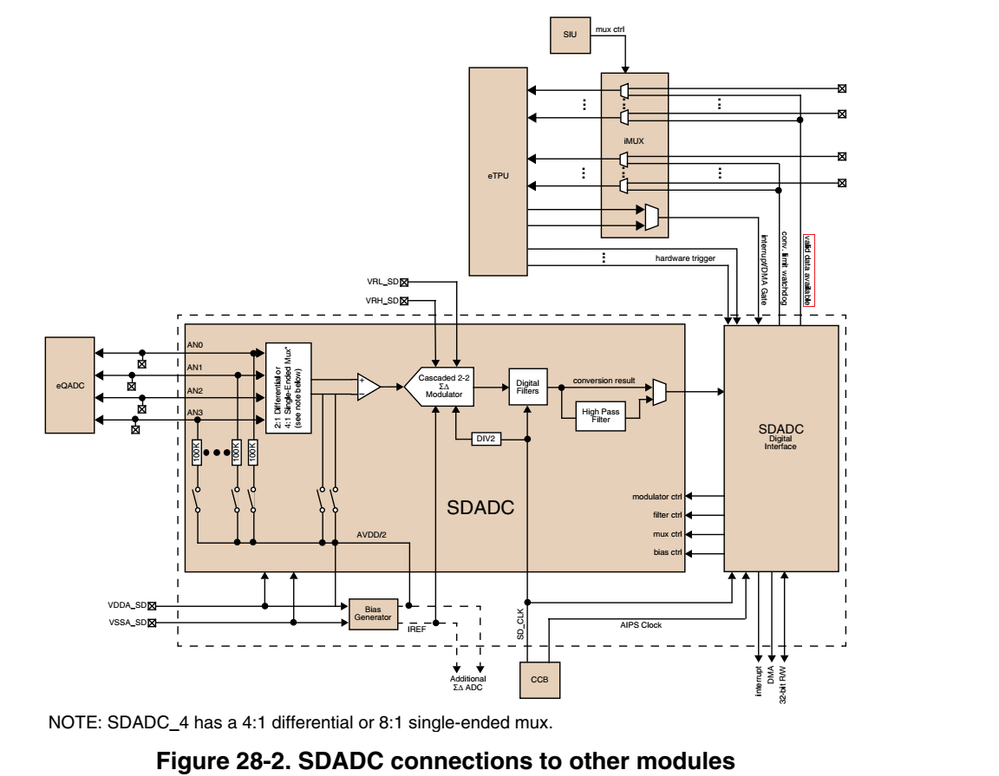

As I know, the input of ETPU channel can be connected from the SDADC valid data flag output or the external pad, we use the SIU_SDETPUA, SIU_SDETPUB, SIU_SDETPUC to choose the connection .You can see the below image:

- I use ETPUA channel 9:

+ In the case 1, ETPUA_9 is connected to the external pad, the pinstate returned by fs_etpu_gpio_pin_history is correct as expected.

+ In the case 2, ETPUA_9 is connected to the SDADC1 data valid flag output, the pinstate returned by fs_etpu_gpio_pin_history always be 0 even though the SDADC1 Conversion Data Valid Event is enabled(CDVEE bit of SDADC_RSER is 1) and Converted Data Valid Flag is 1(CDVF bit of SDADC_SFR is 1). This is wrong. I don't know why.

- The difference between these 2 cases is just SIU_SDETPUA configuraion.

Do you know why?

Regards,

Tam

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Sorry, the ETPU channel is ETPUA_15

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

I tried with 2 cases:

- The ETPUA_15 channel with SDADC2

- The ETPUA_9 channel with SDADC1.

The pinstate always be 0.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi, please create new thread here on the community space or new case according to following procedure:

https://community.nxp.com/docs/DOC-329745