- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- MCX Microcontrollers

- :

- Re: SmartDMA documentation for RT595

SmartDMA documentation for RT595

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

SmartDMA documentation for RT595

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

With the RT595, I need to use DMA to rapidly copy data from FlexIO to a RAM buffer, and the documentation says I should use SmartDMA for this. The RT595 reference manual (Rev 2 of 12/2023) chapter 17 is only one page long and appears to stop abruptly. The majority of the documentation is not there. Where is the documentation for SmartDMA in the RT575? I see NXP has posted the SmartDMA cookbook, and a few very specific app notes. There is also a very minimal API document, clearly also unfinished. I do not see links to any secure document. How do I get a reference-manual level description of this peripheral?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I also couldn't find information about a public, reference-manual-level details the SmartDMA registers and architecture, here are some comments from the relevant team after double checking:

- The SmartDMA is a programmable coprocessor designed to offload the main Arm processor by handling complex, I/O-driven tasks and data manipulation, which is why it is required for use with the FlexIO peripheral instead of the standard DMA controller.

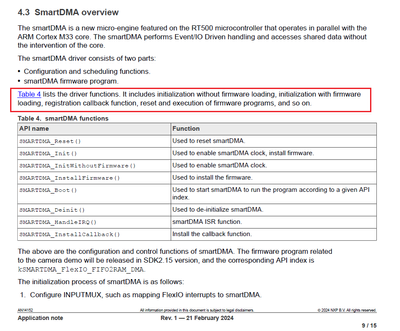

- Unlike a traditional DMA controller that is configured through registers, the SmartDMA executes a dedicated firmware program to perform its function .The smartDMA driver consists of two parts:

• Configuration and scheduling functions.

• smartDMA firmware program

The execution program flow of smartDMA is as follows:

1. Set the parameters of the specific function of the firmware program to be executed.

2. Call SMARTDMA_Reset() to reset smartDMA.

3. Call SMARTDMA_Boot() to start smartDMA to run the given program based on the API index.

4. After the smartDMA execution is completed, an interrupt signal is generated to notify the Arm core that the execution is completed.

Details in the below AN, section 4.3 SmartDMA overview: Using FlexIO and SmartDMA to Emulate Parallel Camera Interface on i.MX RT500

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

These general comments posted by @Sam_Gao are once again not a proper response to our question. It is wholly insufficient for an NXP employee to post he cannot find public documentation, as a follow-up to writing a few weeks earlier that he could not find public documentation. What we need is documentation that covers how to use DMA with FlexIO. This presumably means full documentation of SmartDMA. The Application note mentioned is one of those mentioned on a previous post, and we have already said that this is not at all general documentation of SmartDMA. We still have no list of DMA triggers or DMA pacing requests for FlexIO, and not nearly enough information to generate firmware for the SmartDMA coprocessor.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I couldn't find information about a reference manual containing a complete register map or bit-level programming model for the i.MX RT595 SmartDMA.

The reference-manual level documentation with detailed register maps for the i.MX RT595 SmartDMA is not publicly available, as the intended use is through a high-level API with pre-compiled firmware.

Here is a summary of the available information and the intended usage model based on the documentation:

- SmartDMA API User Guide (IMXRT500SDMAAPIUG): This is the primarysoftware development. It details the API functions used to initialize, control, and interact with the SmartDMA. It includes function prototypes for initialization (

SMARTDMA_Init), loading firmware (SMARTDMA_InstallFirmware), and starting operations (SMARTDMA_Boot), - Application Notes :AN14650, AN13942, AN14152

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This is not a satisfactory solution. I was aware of all these sources before getting your answer, and got almost exactly the same response from you as I previously received from an AI chat bot. All one can do with these application notes is to make an exact copy of the project described. The API documentation is incomplete, and the chapter on SmartDMA stops mid -sentence after less than one page. Meanwhile the documentation for the FlexIO says we must use SmartDMA. Nowhere is there any instruction for how to do this unless I want to reproduce the camera examples. We have no list of DMA triggers or request sources. This situation is totally unusable. Here I am midway through a project, the hardware is there and there is no support from the manufacturer ANYWHERE of how to use DMA for a non-standard FlexIO application. This is just too unreasonable. What on earth can I do now? restart the project with an ST microcontroller? NXP must, MUST provide documentation for the SmartDMA, at the very least, provide a complete API document that lists all the functions and structures, but preferably gives a full list of registers. The present situation is unreasonable and unbearable, and your response is woefully unsatisfactory. At the very least, how does NXP account for the abrupt abandonment of its chapter on SmartDMA in the reference manual?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

'Q1. 'At the very least, how does NXP account for the abrupt abandonment of its chapter on SmartDMA in the reference manual?'

-->This question is out of my scope, and I cannot give a definitive answer. I need to try to find the relevant team and product owner, but I'm not sure if I can, as re-org or unanswerable issues are common.

Q2. The API documentation is incomplete, and the chapter on SmartDMA stops mid -sentence after less than one page. Meanwhile the documentation for the FlexIO says we must use SmartDMA. Nowhere is there any instruction for how to do this unless I want to reproduce the camera examples. We have no list of DMA triggers or request sources. This situation is totally unusable. Here I am midway through a project, the hardware is there and there is no support from the manufacturer ANYWHERE of how to use DMA for a non-standard FlexIO application. This is just too unreasonable.

--> How did you arrive at this conclusion?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sam_Gao of NXP has asked how I reached the conclusion that "the documentation for the FlexIO says we must use SmartDMA"

My answer is that in the RT595 reference manual rev 2 page 2171 we see the following:

51.1.2 DMA Support

On this device, the standard DMA is not supported for use with the FLEXIO module. The SmartDMA should be used instead. Any reference to the standard DMA should be disregarded in the chapter.