- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- MCUXpresso Software and Tools

- :

- MCUXpresso SDK

- :

- Re: 9 bit UART and DMA

9 bit UART and DMA

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

9 bit UART and DMA

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi everyone,

I'm developing a project based on K66, using MCUXpresso 11.2.0 and SDK 2.6.

I have to implement a serial protocol that uses 9 bit data length (with the ninth bit acting as address mark). I modified the uart drivers (fsl_uart and fsl_uart_freertos files) to handle the ninth bit (and to add a timeout handling): now everything is working fine.

Nevertheless the uart speed is high (125000 bps) and the UART used have an only 1 byte FIFO depth (UART4), so the character length is 88 µs: every character received an interrupt must be serviced. Sometimes it happens that a character is lost (and therefore all the packet is lost since there is a crc check) due to a delay in servicing the interrupt request, even if the UART interrupt priority is the highest (maybe this is caused by the FreeRTOS scheduler that can disable the interrupts for a little time).

In another application where the 8 bit data length is used, I developed an UART FreeRTOS driver that uses DMA that is working great.

My question is: can the UART DMA driver (even without FreeRTOS) handle the 9 bit data lenght? I've searched informations about it in the K66 reference manual and online, but with non success.

Many thanks

Biafra

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Francesco and Confused Cake,

You could do it the following way:

The C3 register that contains the 9 bit is contiguous to the data register, so you could set the DMA transmission for two bytes width and filter the C3 register to only take the R8 or T8 bit depending on if you are receiving or transmitting.

I will suggest checking how the LPUART_ReceiveEDMA/LPUART_TransmitEDMA configure the DMA and modify the byte width and change the Date address for the C3 address.

Best Regards,

Alexis Andalon

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I already modified the API on fsl_uart and fsl_uart_freertos files to handle the talktosonic 9 bit communication (and a tx/rx timeout) and it's working, but sometimes a character is lost. I think the reason is because it can't handle interrupts in time (speed is 125000 bps and the UART4 peripheral have only 1 byte FIFO); so I'd want to use DMA.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Francesco,

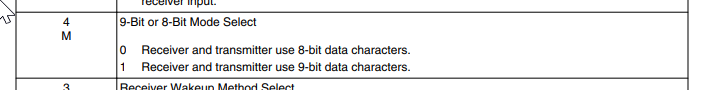

In the LPUARTx_CTRL the M bit is used to enable the 9-bit data character, unfortunately in the SDK still there isn't support for 9-bit communication, so you will need to modify the APIs and type data to support it.

Best Regards,

Alexis Andalon

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi nxf46116,

Many thanks for your answer, sorry for the late processing, but I was on holiday until this morning.

I don't use LPUART, I use UART (UART4).

I already modified the API on fsl_uart and fsl_uart_freertos files to handle the 9 bit communication (and a tx/rx timeout) and it's working, but sometimes a character is lost. I think the reason is because it can't handle interrupts in time (speed is 125000 bps and the UART4 peripheral have only 1 byte FIFO); so I'd want to use DMA.

I already developed a UART FreeRTOS driver that uses DMA for an application that uses 8 bit communication.

My doubt is if the DMA peripheral can handle the UART 9 bit communication.

Many thanks

Biafra

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Francesco,

Should be possible to adapt the 9 bit UART with DMA if you adapt it to transfer the two bytes per transfer.

Best Regards,

Alexis Andalon

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Alexis,

I wanted to check the feasibility of a 16-bit access to the UART C3 register in order to write/read also the UART D register with a single 16-bit access like DMA would do.

I started modifying the UART_WriteBlocking() function in the fsl_uart.c SDK UART driver source file in order to transmit 9-bit data in blocking mode.

#define ACCESS_16_BIT // enable 16-bit access to UART C3/D registers

typedef union

{

unsigned short WORD;

struct { unsigned char L, H;} BYTE;

} ACC16_UNION;

/*!

* @brief Writes to the TX register using a blocking method.

*

* This function polls the TX register, waits for the TX register to be empty or for the TX FIFO

* to have room and writes data to the TX buffer.

*

* @note This function does not check whether all data is sent out to the bus.

* Before disabling the TX, check kUART_TransmissionCompleteFlag to ensure that the TX is

* finished.

*

* @param base UART peripheral base address.

* @param data Start address of the data to write.

* @param length Size of the data to write.

* @param data9bit Start addresss of the ninth bit to write.

*/

void UART_WriteBlocking(UART_Type *base, const uint8_t *data, size_t length, const uint8_t *data9bit)

{

#ifdef ACCESS_16_BIT

ACC16_UNION u;

uint16_t *p = (uint16_t *)&base->C3;

#endif

/* This API can only ensure that the data is written into the data buffer but can't

ensure all data in the data buffer are sent into the transmit shift buffer. */

while (length--)

{

while (!(base->S1 & UART_S1_TDRE_MASK))

{

}

if( data9bit != NULL )

{

#ifdef ACCESS_16_BIT

u.BYTE.L = base->C3;

if( *(data9bit++) )

u.BYTE.L |= UART_C3_T8_MASK;

else

u.BYTE.L &= ~UART_C3_T8_MASK;

u.BYTE.H = *(data++);

*p = u.WORD;

#else

if( *(data9bit++) )

base->C3 |= UART_C3_T8_MASK;

else

base->C3 &= ~UART_C3_T8_MASK;

base->D = *(data++);

#endif

}

else

{

base->D = *(data++);

}

}

}

But the instruction:

*p = u.WORD;

generates a Hard Fault error. The effective write access is executed with the following assembler instruction:

strh r2, [r3, #0]

where R2 contains the 16-bit value to write at the address holded by R3. Both UART C3 and D registers remain not changed.

I wanted to make this test, because I just wrote code to configure DMA for a 16-bit write transfer to the UART C3/D registers, but when I start the transfer I get no hard fault neither no DMA transfer completed interrupt and nothing is transmitted from the UART TX pin.

It looks like those UART registers (at least) must be individually accessed. Is there any way (in compile-time or run-time) to achieve that?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi nxf46116,

I think this can be the way, but how to configure the DMA peripheral to put the ninth bit in the second byte?

Many thanks

Biafra