- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- MCUXpresso Software and Tools

- :

- MCUXpresso IDE

- :

- Re: Linker Script Changes Error in MCUxpresso 11.0.0

Linker Script Changes Error in MCUxpresso 11.0.0

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Linker Script Changes Error in MCUxpresso 11.0.0

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hey Guys,

I faced a huge problem while exporting my projects from version 10.3.1 to version 11.0.0.

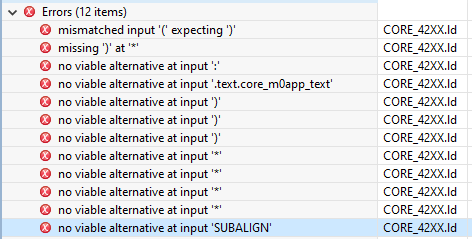

Importing went good but the Project would not build. Showcasing the error

PROGRAM_FLASH: 324296 B 472 KB 67.10%

SRAM_UPPER: 124092 B 65472 B 189.53%

SRAM_LOWER: 0 GB 65520 B 0.00%

c:/nxp/mcuxpressoide_11.0.0_2516/ide/plugins/com.nxp.mcuxpresso.tools.win32_11.0.0.201905131304/tools/bin/../lib/gcc/arm-none-eabi/8.2.1/../../../../arm-none-eabi/bin/ld.exe: region `SRAM_UPPER' overflowed by 58620 bytes

The project is a FreeRTOS project using the HEAP 5 memory scheme which has different memory location we can assign.

Anyhow, the issue was that the auto-generated Linker File(*.ld file) was adding '.' at the end of the section names, you describe in the MCU settings as shown below

VERSION 11.

.noinit_RAM2 (NOLOAD) :

{

. = ALIGN(4) ;

*(.noinit.$RAM2)

*(.noinit.$SRAM_LOWER)

*(.noinit.$RAM2.*)

*(.noinit.$SRAM_LOWER.*)

. = ALIGN(4) ;

} > SRAM_LOWER

the same section in Version 10.3.1

.noinit_RAM2 (NOLOAD) : ALIGN(4)

{

*(.noinit.$RAM2*)

*(.noinit.$SRAM_LOWER*)

. = ALIGN(4) ;

} > SRAM_LOWER

The FreeRTOS heap5 file is where we mention the array size and name

static __attribute__ ((used,section(".noinit.$SRAM_LOWER_Heap5"))) uint8_t heap_sram_lower[60*1024]; /* placed in in no_init section inside SRAM_LOWER */

static __attribute__ ((used,section(".noinit_Heap5"))) uint8_t heap_sram_upper[20*1024]; /* placed in in no_init section inside SRAM_UPPER */

These arrays where not being recognized by the linker and hence producing the overflowed error.

Once I changed the name of the arrays to add '.' it fixed the problem.

changed Named

static __attribute__ ((used,section(".noinit.$SRAM_LOWER._Heap5"))) uint8_t heap_sram_lower[63*1024]; /* placed in in no_init section inside SRAM_LOWER */

static __attribute__ ((used,section(".noinit_Heap5."))) uint8_t heap_sram_upper[28*1024]; /* placed in in no_init section inside SRAM_UPPER */

I don't know why that addition of character "." was added to the linker scripts. Slightly annoying when you are exporting to an updated version.

Please give a way to remove that feature for backward compatibility. So we don't have to make this small change on all the projects and branches of them.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The addition of the "." was one of the intentional changes made to the linker script system in MCUXpresso IDE v11.0.0 (these are mentioned inMCUXpresso IDE v11.0.0 Now Available ).

I'm sorry that in your case this triggered a problem - but certainly the "correct" fix for your specific case is to change your section attribute definition, as you have already found.

Regards,

MCUXpresso IDE Support

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It appears that the XText nature which was added to support freemarker syntax coloring does not handle comments in the link scripts gracefully. I have migrated several LPCXpresso projects into MCUXpresso and found several of the internally generated linker stubs (where comments already exist) are not parsed by the freemarker xtext grammar properly. Keep in mind these are comments which already existed in the default linker templates. I did not add them.

The actual build generates binaries, but the project remains in an error state which undoubtedly WILL affect our automated build tools which rely on the command line compiler. What do you propose as a fix for this problem?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

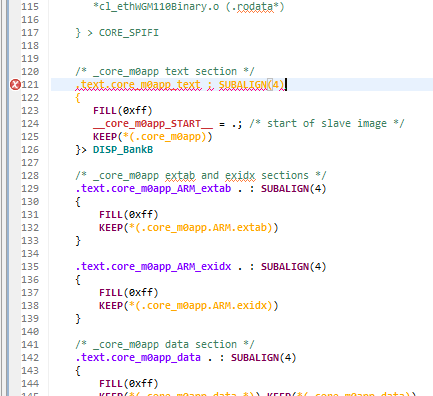

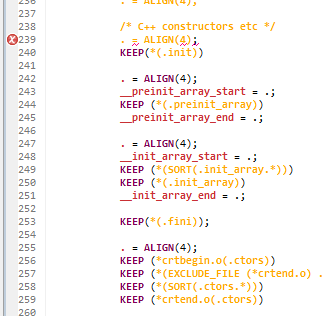

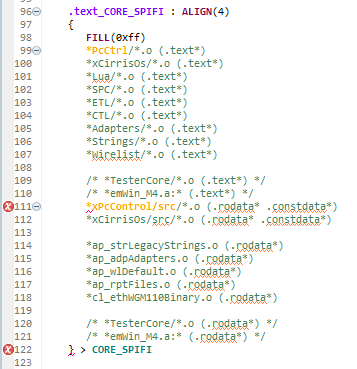

After further experiments, I am reasonably certain that the xText parser for LD linker scripts is not working properly. It appears that the parser gets hung up on wildcards in path names (because the syntax contains the multi-line comment sequence "/*". The xtext parser obviously believes I have a multi-line comment starting on Lin 99. The parser does not recover again until line 111, and then gets thrown off into another multi-line comment which continues on until line 122.

I like the idea of making the LD scripts more readable, but if you are only going to support a subset of the LD syntax, that's a non-starter in my opinion. I used to write xText grammars and gave up on situations like this when the grammar attempted to implement an already-existing parsed language that is not actually implemented with xText under the hood in the GNU tools (in this example, LD). There were just too many corner cases to be able to support, and there was no way to pull some of those cases off using what existed at the time with xText. If you are making your own language from scratch, xText works very well. Either way, I hope you are able to fix this problem, or have a workaround you can propose for us.

I attempted to remove the XText nature from my project, but no luck. The project still has errors even though the output executables are generated and valid.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Does this help? https://community.nxp.com/thread/527820

BTW: This is part of the Eclipse CDT project, and so you might get more help there.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

That did the trick on my workstation. I have yet to see if this will also work on our build server which invokes mcuxpresso (used to be lpcxpresso) from the command line. I don't see it preserving the setting in the project file. Thanks for the workaround!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Brad,

>That did the trick on my workstation.

You mean changing the editor for the .ld files?

The linker script coloring is independent of the build system (it is for the editor view only), so should not affect your build.

As for the affected .ld files: would you mind posting them here? That way the IDE engineering team could check why parsing them failed (instead trying from your screenshots).

Erich

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes Erich, I changed the editor for the *.ld files. That's good news about the errors not affecting builds, although it is kind of annoying to have any errors exist in the project at all when nothing is problematic to the actual toolchains. I hope you can fix it, but after working with Xtext in the past, I have my doubts. Hopefully they have made some improvements to the framework.

Here is my linker script:

/*

* GENERATED FILE - DO NOT EDIT

* Copyright (c) 2008-2013 Code Red Technologies Ltd,

* Copyright 2015, 2018-2019 NXP

* (c) NXP Semiconductors 2013-2020

* Generated linker script file for LPC4367

* Created from linkscript.ldt by FMCreateLinkLibraries

* Using Freemarker v2.3.23

* MCUXpresso IDE v11.2.0 [Build 4120] [2020-07-09] on Aug 19, 2020 7:42:08 PM

*

* List of predefined variables and values:

* basename = FMCreateLinkLibraries

* bss_align = 4

* buildConfig = 42XX

* chipFamily = LPC43xx

* chipName = LPC4367

* CODE = CORE_BankA

* configMemory[]

* configMemory[0] = name=CORE_BankA alias=Flash location=0x1a000000 size=0x80000 sizek=512K bytes mcuPattern=Flash flash=true RAM=false defaultFlash=true defaultRAM=false

* configMemory[1] = name=CORE_SPIFI alias=Flash2 location=0x15000000 size=0x1000000 sizek=16M bytes mcuPattern=Flash flash=true RAM=false defaultFlash=false defaultRAM=false

* configMemory[2] = name=CORE_SDRAM alias=RAM location=0x28800000 size=0x800000 sizek=8M bytes mcuPattern=RAM flash=false RAM=true defaultFlash=false defaultRAM=true

* configMemory[3] = name=DISP_BankB alias=Flash3 location=0x1b000000 size=0x80000 sizek=512K bytes mcuPattern=Flash flash=true RAM=false defaultFlash=false defaultRAM=false

* configMemory[4] = name=DISP_SPIFI alias=Flash4 location=0x14000000 size=0x1000000 sizek=16M bytes mcuPattern=Flash flash=true RAM=false defaultFlash=false defaultRAM=false

* configMemory[5] = name=RamLoc32 alias=RAM2 location=0x10000000 size=0x8000 sizek=32K bytes mcuPattern=RAM flash=false RAM=true defaultFlash=false defaultRAM=false

* configMemory[6] = name=RamLoc40 alias=RAM3 location=0x10080000 size=0xa000 sizek=40K bytes mcuPattern=RAM flash=false RAM=true defaultFlash=false defaultRAM=false

* configMemory[7] = name=RamAHB32 alias=RAM4 location=0x20000000 size=0x8000 sizek=32K bytes mcuPattern=RAM flash=false RAM=true defaultFlash=false defaultRAM=false

* configMemory[8] = name=RamAHB16 alias=RAM5 location=0x20008000 size=0x4000 sizek=16K bytes mcuPattern=RAM flash=false RAM=true defaultFlash=false defaultRAM=false

* configMemory[9] = name=RamAHB_ETB16 alias=RAM6 location=0x2000c000 size=0x4000 sizek=16K bytes mcuPattern=RAM flash=false RAM=true defaultFlash=false defaultRAM=false

* DATA = CORE_SDRAM

* data_align = 4

* date = Wed Aug 19 19:42:08 MDT 2020

* environment (hash)

* extraSections[]

* Flash = CORE_BankA

* Flash2 = CORE_SPIFI

* Flash3 = DISP_BankB

* Flash4 = DISP_SPIFI

* HEAP_STACK_STYLE = lpc

* heap_symbol = _pvHeapStart

* inclistbase = C:\nxp\MCUXpressoIDE_11.2.0_4120\ide\configuration\org.eclipse.osgi\4\0\.cp\Data\libinc\newlibnano_nohost_cpp

* inclistbasename = newlibnano_nohost_cpp

* inclisttype = newlibnano_nohost_cpp

* isCppProject = true

* isSlave = false

* libraries[]

* libraries[0] = libgcc.a

* libraries[1] = libc_nano.a

* libraries[2] = libstdc++_nano.a

* libraries[3] = libm.a

* libraries[4] = libcr_newlib_nohost.a

* libraries[5] = crti.o

* libraries[6] = crtn.o

* libraries[7] = crtbegin.o

* libraries[8] = crtend.o

* library_include = CORE_42XX_library.ld

* libtype = NewlibNano (nohost)

* LINK_TO_RAM = false

* listvars = true

* memory_include = CORE_42XX_memory.ld

* MemUtils (hash)

* numCores = 3

* PLAIN_LOAD_IMAGE = false

* procFamily = Cortex-M

* procName = Cortex-M4

* project = CORE

* RAM = CORE_SDRAM

* RAM2 = RamLoc32

* RAM3 = RamLoc40

* RAM4 = RamAHB32

* RAM5 = RamAHB16

* RAM6 = RamAHB_ETB16

* script = CORE_42XX.ld

* scriptType = library

* slaveName = Master

* slaves[]

* slaves[0] = name=M0APP objectPath=${workspace_loc:/DISP/Debug/Debug.axf.o} linkSection=DISP_BankB runtimeSection= textSection=.core_m0app textSectionNormalized=_core_m0app dataStartSymbol=__start_data dataEndSymbol=__end_data enabled=true;

* STACK_OFFSET = 0

* stack_section = CORE_SDRAM

* start_symbol = ResetISR

* systemProperties (hash)

* text_align = 4

* Utils (hash)

* version = MCUXpresso IDE v11.2.0 [Build 4120] [2020-07-09]

* workspace_loc = C:/Dev/Embedded/MCUXpresso

* year = 2020

*/

INCLUDE "CORE_42XX_library.ld"

INCLUDE "CORE_42XX_memory.ld"

ENTRY(ResetISR)

SECTIONS

{

.text_CORE_SPIFI : ALIGN(4)

{

FILL(0xff)

*PcCtrl/*.o (.text*)

*xCirrisOs/*.o (.text*)

*Lua/*.o (.text*)

*SPC/*.o (.text*)

*ETL/*.o (.text*)

*CTL/*.o (.text*)

*Adapters/*.o (.text*)

*Strings/*.o (.text*)

*Wirelist/*.o (.text*)

/* *TesterCore/*.o (.text*) */

/* *emWin_M4.a:* (.text*) */

*xPcControl/src/*.o (.rodata* .constdata*)

*xCirrisOs/src/*.o (.rodata* .constdata*)

*ap_strLegacyStrings.o (.rodata*)

*ap_adpAdapters.o (.rodata*)

*ap_wlDefault.o (.rodata*)

*ap_rptFiles.o (.rodata*)

*cl_ethWGM110Binary.o (.rodata*)

/* *TesterCore/*.o (.rodata*) */

/* *emWin_M4.a:* (.rodata*) */

} > CORE_SPIFI

/* _core_m0app text section */

.text.core_m0app_text : SUBALIGN(4)

{

FILL(0xff)

__core_m0app_START__ = .; /* start of slave image */

KEEP(*(.core_m0app))

}> DISP_BankB

/* _core_m0app extab and exidx sections */

.text.core_m0app_ARM_extab . : SUBALIGN(4)

{

FILL(0xff)

KEEP(*(.core_m0app.ARM.extab))

}

.text.core_m0app_ARM_exidx . : SUBALIGN(4)

{

FILL(0xff)

KEEP(*(.core_m0app.ARM.exidx))

}

/* _core_m0app data section */

.text.core_m0app_data . : SUBALIGN(4)

{

FILL(0xff)

KEEP(*(.core_m0app.data_*)) KEEP(*(.core_m0app.data))

__core_m0app_END__ = .; /* end of slave image */

/* perform some simple sanity checks */

ASSERT(!(__core_m0app_START__ == __core_m0app_END__), "No slave code for _core_m0app");

ASSERT( (ABSOLUTE(__core_m0app_START__) == __vectors_start___core_m0app), "M0APP execute address differs from address provided in source image");

}

/* Slave SPIFI secondary text section */

.text_DISP_SPIFI : SUBALIGN(4)

{

FILL(0xff)

KEEP(*(.text_DISP_SPIFI))

}> DISP_SPIFI

/* MAIN TEXT SECTION */

.text : ALIGN(4)

{

FILL(0xff)

__vectors_start__ = ABSOLUTE(.) ;

KEEP(*(.isr_vector))

/* Global Section Table */

. = ALIGN(4) ;

__section_table_start = .;

__data_section_table = .;

LONG(LOADADDR(.data));

LONG( ADDR(.data));

LONG( SIZEOF(.data));

LONG(LOADADDR(.data_RAM2));

LONG( ADDR(.data_RAM2));

LONG( SIZEOF(.data_RAM2));

LONG(LOADADDR(.data_RAM3));

LONG( ADDR(.data_RAM3));

LONG( SIZEOF(.data_RAM3));

LONG(LOADADDR(.data_RAM4));

LONG( ADDR(.data_RAM4));

LONG( SIZEOF(.data_RAM4));

LONG(LOADADDR(.data_RAM5));

LONG( ADDR(.data_RAM5));

LONG( SIZEOF(.data_RAM5));

LONG(LOADADDR(.data_RAM6));

LONG( ADDR(.data_RAM6));

LONG( SIZEOF(.data_RAM6));

__data_section_table_end = .;

__bss_section_table = .;

LONG( ADDR(.bss));

LONG( SIZEOF(.bss));

LONG( ADDR(.bss_RAM2));

LONG( SIZEOF(.bss_RAM2));

LONG( ADDR(.bss_RAM3));

LONG( SIZEOF(.bss_RAM3));

LONG( ADDR(.bss_RAM4));

LONG( SIZEOF(.bss_RAM4));

LONG( ADDR(.bss_RAM5));

LONG( SIZEOF(.bss_RAM5));

LONG( ADDR(.bss_RAM6));

LONG( SIZEOF(.bss_RAM6));

__bss_section_table_end = .;

__section_table_end = . ;

/* End of Global Section Table */

*(.after_vectors*)

} > CORE_BankA

.text : ALIGN(4)

{

*(EXCLUDE_FILE(*PcCtrl/*.o) .text*)

*(EXCLUDE_FILE(*xCirrisOs/*.o) .text*)

*(EXCLUDE_FILE(*Lua/*.o) .text*)

*(EXCLUDE_FILE(*SPC/*.o) .text*)

*(EXCLUDE_FILE(*ETL/*.o) .text*)

*(EXCLUDE_FILE(*CTL/*.o) .text*)

*(EXCLUDE_FILE(*Adapters/*.o) .text*)

*(EXCLUDE_FILE(*Strings/*.o) .text*)

*(EXCLUDE_FILE(*Wirelist/*.o) .text*)

/* *(EXCLUDE_FILE(*TesterCore/*.o) .text*) */

/* *(EXCLUDE_FILE(*emWin_M4.a:*) .text*) */

*(EXCLUDE_FILE(*bd_fwFirmwareMgr.o *iap_18xx_43xx.o *romapi_18xx_43xx.o *rgu_18xx_43xx.o) .text*)

*(EXCLUDE_FILE(*xPcControl/src/*.o) .rodata* .constdata*)

*(EXCLUDE_FILE(*xCirrisOs/src/*.o) .rodata* .constdata*)

*(EXCLUDE_FILE(*ap_strLegacyStrings.o) .rodata*)

*(EXCLUDE_FILE(*ap_adpAdapters.o) .rodata*)

*(EXCLUDE_FILE(*ap_wlDefault.o) .rodata*)

*(EXCLUDE_FILE(*ap_rptFiles.o) .rodata*)

*(EXCLUDE_FILE(*cl_ethWGM110Binary.o) .rodata*)

/* *(EXCLUDE_FILE(*TesterCore/*.o) .rodata*) */

/* *(EXCLUDE_FILE(*emWin_M4.a:*) .rodata*) */

*(EXCLUDE_FILE(*bd_fwFirmwareMgr.o *iap_18xx_43xx.o *romapi_18xx_43xx.o *rgu_18xx_43xx.o) .rodata)

*(EXCLUDE_FILE(*bd_fwFirmwareMgr.o *iap_18xx_43xx.o *romapi_18xx_43xx.o *rgu_18xx_43xx.o) .rodata.*)

*(EXCLUDE_FILE(*bd_fwFirmwareMgr.o *iap_18xx_43xx.o *romapi_18xx_43xx.o *rgu_18xx_43xx.o) .constdata)

*(EXCLUDE_FILE(*bd_fwFirmwareMgr.o *iap_18xx_43xx.o *romapi_18xx_43xx.o *rgu_18xx_43xx.o) .constdata.*)

. = ALIGN(4);

/* C++ constructors etc */

. = ALIGN(4);

KEEP(*(.init))

. = ALIGN(4);

__preinit_array_start = .;

KEEP (*(.preinit_array))

__preinit_array_end = .;

. = ALIGN(4);

__init_array_start = .;

KEEP (*(SORT(.init_array.*)))

KEEP (*(.init_array))

__init_array_end = .;

KEEP(*(.fini));

. = ALIGN(4);

KEEP (*crtbegin.o(.ctors))

KEEP (*(EXCLUDE_FILE (*crtend.o) .ctors))

KEEP (*(SORT(.ctors.*)))

KEEP (*crtend.o(.ctors))

. = ALIGN(4);

KEEP (*crtbegin.o(.dtors))

KEEP (*(EXCLUDE_FILE (*crtend.o) .dtors))

KEEP (*(SORT(.dtors.*)))

KEEP (*crtend.o(.dtors))

. = ALIGN(4);

/* End C++ */

} > CORE_BankA

/*

* for exception handling/unwind - some Newlib functions (in common

* with C++ and STDC++) use this.

*/

.ARM.extab : ALIGN(4)

{

*(.ARM.extab* .gnu.linkonce.armextab.*)

} > CORE_BankA

.ARM.exidx : ALIGN(4)

{

__exidx_start = .;

*(.ARM.exidx* .gnu.linkonce.armexidx.*)

__exidx_end = .;

} > CORE_BankA

_etext = .;

/* DATA section for RamLoc32 */

.data_RAM2 : ALIGN(4)

{

FILL(0xff)

PROVIDE(__start_data_RAM2 = .) ;

PROVIDE(__start_data_RamLoc32 = .) ;

*(.ramfunc.$RAM2)

*(.ramfunc.$RamLoc32)

*(.data.$RAM2)

*(.data.$RamLoc32)

*(.data.$RAM2.*)

*(.data.$RamLoc32.*)

. = ALIGN(4) ;

PROVIDE(__end_data_RAM2 = .) ;

PROVIDE(__end_data_RamLoc32 = .) ;

} > RamLoc32 AT>CORE_BankA

/* DATA section for RamLoc40 */

.data_RAM3 : ALIGN(4)

{

FILL(0xff)

PROVIDE(__start_data_RAM3 = .) ;

PROVIDE(__start_data_RamLoc40 = .) ;

*(.ramfunc.$RAM3)

*(.ramfunc.$RamLoc40)

*(.data.$RAM3)

*(.data.$RamLoc40)

*(.data.$RAM3.*)

*(.data.$RamLoc40.*)

. = ALIGN(4) ;

PROVIDE(__end_data_RAM3 = .) ;

PROVIDE(__end_data_RamLoc40 = .) ;

} > RamLoc40 AT>CORE_BankA

/* DATA section for RamAHB32 */

.data_RAM4 : ALIGN(4)

{

FILL(0xff)

PROVIDE(__start_data_RAM4 = .) ;

PROVIDE(__start_data_RamAHB32 = .) ;

*(.ramfunc.$RAM4)

*(.ramfunc.$RamAHB32)

*(.data.$RAM4)

*(.data.$RamAHB32)

*(.data.$RAM4.*)

*(.data.$RamAHB32.*)

. = ALIGN(4) ;

PROVIDE(__end_data_RAM4 = .) ;

PROVIDE(__end_data_RamAHB32 = .) ;

} > RamAHB32 AT>CORE_BankA

/* DATA section for RamAHB16 */

.data_RAM5 : ALIGN(4)

{

FILL(0xff)

PROVIDE(__start_data_RAM5 = .) ;

PROVIDE(__start_data_RamAHB16 = .) ;

*(.ramfunc.$RAM5)

*(.ramfunc.$RamAHB16)

*(.data.$RAM5)

*(.data.$RamAHB16)

*(.data.$RAM5.*)

*(.data.$RamAHB16.*)

. = ALIGN(4) ;

PROVIDE(__end_data_RAM5 = .) ;

PROVIDE(__end_data_RamAHB16 = .) ;

} > RamAHB16 AT>CORE_BankA

/* DATA section for RamAHB_ETB16 */

.data_RAM6 : ALIGN(4)

{

FILL(0xff)

PROVIDE(__start_data_RAM6 = .) ;

PROVIDE(__start_data_RamAHB_ETB16 = .) ;

*(.ramfunc.$RAM6)

*(.ramfunc.$RamAHB_ETB16)

*(.data.$RAM6)

*(.data.$RamAHB_ETB16)

*(.data.$RAM6.*)

*(.data.$RamAHB_ETB16.*)

. = ALIGN(4) ;

PROVIDE(__end_data_RAM6 = .) ;

PROVIDE(__end_data_RamAHB_ETB16 = .) ;

} > RamAHB_ETB16 AT>CORE_BankA

/* MAIN DATA SECTION */

.uninit_RESERVED (NOLOAD) : ALIGN(4)

{

_start_uninit_RESERVED = .;

KEEP(*(.bss.$RESERVED*))

. = ALIGN(4) ;

_end_uninit_RESERVED = .;

} > CORE_SDRAM AT> CORE_SDRAM

/* Main DATA section (CORE_SDRAM) */

.data : ALIGN(4)

{

FILL(0xff)

_data = . ;

PROVIDE(__start_data_RAM = .) ;

PROVIDE(__start_data_CORE_SDRAM = .) ;

*(vtable)

*(.ramfunc*)

KEEP(*(CodeQuickAccess))

KEEP(*(DataQuickAccess))

*(RamFunction)

*bd_fwFirmwareMgr.o(.text*)

*bd_fwFirmwareMgr.o(.rodata .rodata.* .constdata .constdata.*)

*iap_18xx_43xx.o(.text*)

*iap_18xx_43xx.o(.rodata .rodata.* .constdata .constdata.*)

*romapi_18xx_43xx.o(.text*)

*romapi_18xx_43xx.o(.rodata .rodata.* .constdata .constdata.*)

*rgu_18xx_43xx.o(.text*)

*rgu_18xx_43xx.o(.rodata .rodata.* .constdata .constdata.*)

. = ALIGN(4);

*(.data*)

. = ALIGN(4) ;

_edata = . ;

PROVIDE(__end_data_RAM = .) ;

PROVIDE(__end_data_CORE_SDRAM = .) ;

} > CORE_SDRAM AT>CORE_BankA

/* BSS section for RamLoc32 */

.bss_RAM2 : ALIGN(4)

{

PROVIDE(__start_bss_RAM2 = .) ;

PROVIDE(__start_bss_RamLoc32 = .) ;

*(.bss.$RAM2)

*(.bss.$RamLoc32)

*(.bss.$RAM2.*)

*(.bss.$RamLoc32.*)

. = ALIGN (. != 0 ? 4 : 1) ; /* avoid empty segment */

PROVIDE(__end_bss_RAM2 = .) ;

PROVIDE(__end_bss_RamLoc32 = .) ;

} > RamLoc32 AT> RamLoc32

/* BSS section for RamLoc40 */

.bss_RAM3 : ALIGN(4)

{

PROVIDE(__start_bss_RAM3 = .) ;

PROVIDE(__start_bss_RamLoc40 = .) ;

*(.bss.$RAM3)

*(.bss.$RamLoc40)

*(.bss.$RAM3.*)

*(.bss.$RamLoc40.*)

. = ALIGN (. != 0 ? 4 : 1) ; /* avoid empty segment */

PROVIDE(__end_bss_RAM3 = .) ;

PROVIDE(__end_bss_RamLoc40 = .) ;

} > RamLoc40 AT> RamLoc40

/* BSS section for RamAHB32 */

.bss_RAM4 : ALIGN(4)

{

PROVIDE(__start_bss_RAM4 = .) ;

PROVIDE(__start_bss_RamAHB32 = .) ;

*(.bss.$RAM4)

*(.bss.$RamAHB32)

*(.bss.$RAM4.*)

*(.bss.$RamAHB32.*)

. = ALIGN (. != 0 ? 4 : 1) ; /* avoid empty segment */

PROVIDE(__end_bss_RAM4 = .) ;

PROVIDE(__end_bss_RamAHB32 = .) ;

} > RamAHB32 AT> RamAHB32

/* BSS section for RamAHB16 */

.bss_RAM5 : ALIGN(4)

{

PROVIDE(__start_bss_RAM5 = .) ;

PROVIDE(__start_bss_RamAHB16 = .) ;

*(.bss.$RAM5)

*(.bss.$RamAHB16)

*(.bss.$RAM5.*)

*(.bss.$RamAHB16.*)

. = ALIGN (. != 0 ? 4 : 1) ; /* avoid empty segment */

PROVIDE(__end_bss_RAM5 = .) ;

PROVIDE(__end_bss_RamAHB16 = .) ;

} > RamAHB16 AT> RamAHB16

/* BSS section for RamAHB_ETB16 */

.bss_RAM6 : ALIGN(4)

{

PROVIDE(__start_bss_RAM6 = .) ;

PROVIDE(__start_bss_RamAHB_ETB16 = .) ;

*(.bss.$RAM6)

*(.bss.$RamAHB_ETB16)

*(.bss.$RAM6.*)

*(.bss.$RamAHB_ETB16.*)

. = ALIGN (. != 0 ? 4 : 1) ; /* avoid empty segment */

PROVIDE(__end_bss_RAM6 = .) ;

PROVIDE(__end_bss_RamAHB_ETB16 = .) ;

} > RamAHB_ETB16 AT> RamAHB_ETB16

/* MAIN BSS SECTION */

.bss : ALIGN(4)

{

_bss = .;

PROVIDE(__start_bss_RAM = .) ;

PROVIDE(__start_bss_CORE_SDRAM = .) ;

*(.bss*)

*(COMMON)

. = ALIGN(4) ;

_ebss = .;

PROVIDE(__end_bss_RAM = .) ;

PROVIDE(__end_bss_CORE_SDRAM = .) ;

PROVIDE(end = .);

} > CORE_SDRAM AT> CORE_SDRAM

/* NOINIT section for RamLoc32 */

.noinit_RAM2 (NOLOAD) : ALIGN(4)

{

PROVIDE(__start_noinit_RAM2 = .) ;

PROVIDE(__start_noinit_RamLoc32 = .) ;

*(.noinit.$RAM2)

*(.noinit.$RamLoc32)

*(.noinit.$RAM2.*)

*(.noinit.$RamLoc32.*)

. = ALIGN(4) ;

PROVIDE(__end_noinit_RAM2 = .) ;

PROVIDE(__end_noinit_RamLoc32 = .) ;

} > RamLoc32 AT> RamLoc32

/* NOINIT section for RamLoc40 */

.noinit_RAM3 (NOLOAD) : ALIGN(4)

{

PROVIDE(__start_noinit_RAM3 = .) ;

PROVIDE(__start_noinit_RamLoc40 = .) ;

*(.noinit.$RAM3)

*(.noinit.$RamLoc40)

*(.noinit.$RAM3.*)

*(.noinit.$RamLoc40.*)

. = ALIGN(4) ;

PROVIDE(__end_noinit_RAM3 = .) ;

PROVIDE(__end_noinit_RamLoc40 = .) ;

} > RamLoc40 AT> RamLoc40

/* NOINIT section for RamAHB32 */

.noinit_RAM4 (NOLOAD) : ALIGN(4)

{

PROVIDE(__start_noinit_RAM4 = .) ;

PROVIDE(__start_noinit_RamAHB32 = .) ;

*(.noinit.$RAM4)

*(.noinit.$RamAHB32)

*(.noinit.$RAM4.*)

*(.noinit.$RamAHB32.*)

. = ALIGN(4) ;

PROVIDE(__end_noinit_RAM4 = .) ;

PROVIDE(__end_noinit_RamAHB32 = .) ;

} > RamAHB32 AT> RamAHB32

/* NOINIT section for RamAHB16 */

.noinit_RAM5 (NOLOAD) : ALIGN(4)

{

PROVIDE(__start_noinit_RAM5 = .) ;

PROVIDE(__start_noinit_RamAHB16 = .) ;

*(.noinit.$RAM5)

*(.noinit.$RamAHB16)

*(.noinit.$RAM5.*)

*(.noinit.$RamAHB16.*)

. = ALIGN(4) ;

PROVIDE(__end_noinit_RAM5 = .) ;

PROVIDE(__end_noinit_RamAHB16 = .) ;

} > RamAHB16 AT> RamAHB16

/* NOINIT section for RamAHB_ETB16 */

.noinit_RAM6 (NOLOAD) : ALIGN(4)

{

PROVIDE(__start_noinit_RAM6 = .) ;

PROVIDE(__start_noinit_RamAHB_ETB16 = .) ;

*(.noinit.$RAM6)

*(.noinit.$RamAHB_ETB16)

*(.noinit.$RAM6.*)

*(.noinit.$RamAHB_ETB16.*)

. = ALIGN(4) ;

PROVIDE(__end_noinit_RAM6 = .) ;

PROVIDE(__end_noinit_RamAHB_ETB16 = .) ;

} > RamAHB_ETB16 AT> RamAHB_ETB16

/* DEFAULT NOINIT SECTION */

.noinit (NOLOAD): ALIGN(4)

{

_noinit = .;

PROVIDE(__start_noinit_RAM = .) ;

PROVIDE(__start_noinit_CORE_SDRAM = .) ;

*(.noinit*)

. = ALIGN(4) ;

_end_noinit = .;

PROVIDE(__end_noinit_RAM = .) ;

PROVIDE(__end_noinit_CORE_SDRAM = .) ;

} > CORE_SDRAM AT> CORE_SDRAM

PROVIDE(_pvHeapStart = DEFINED(__user_heap_base) ? __user_heap_base : .);

PROVIDE(_vStackTop = DEFINED(__user_stack_top) ? __user_stack_top : __top_CORE_SDRAM - 0);

/* ## Create checksum value (used in startup) ## */

PROVIDE(__valid_user_code_checksum = 0 -

(_vStackTop

+ (ResetISR + 1)

+ (NMI_Handler + 1)

+ (HardFault_Handler + 1)

+ (( DEFINED(MemManage_Handler) ? MemManage_Handler : 0 ) + 1) /* MemManage_Handler may not be defined */

+ (( DEFINED(BusFault_Handler) ? BusFault_Handler : 0 ) + 1) /* BusFault_Handler may not be defined */

+ (( DEFINED(UsageFault_Handler) ? UsageFault_Handler : 0 ) + 1) /* UsageFault_Handler may not be defined */

) );

/* Provide basic symbols giving location and size of main text

* block, including initial values of RW data sections. Note that

* these will need extending to give a complete picture with

* complex images (e.g multiple Flash banks).

*/

_image_start = LOADADDR(.text);

_image_end = LOADADDR(.data) + SIZEOF(.data);

_image_size = _image_end - _image_start;

}Best wishes, and thanks for your help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I think the simplest way for you to do this is to use the Managed Linker script scheme to override the default template provided in the IDE. Take a copy of

noinit_section.ldt (from C:\nxp\MCUXpressoIDE_11.0.0_2516\ide\Wizards\linker) and place it in a folder in your project called linkscripts

edit this file to remove the offending "."

You should now be ale to build as you expect. For info, see Chapter 18 in the User Guide.