- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- MCUXpresso Software and Tools

- :

- MCUXpresso IDE

- :

- LPC55S69 PLL1 does not function

LPC55S69 PLL1 does not function

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

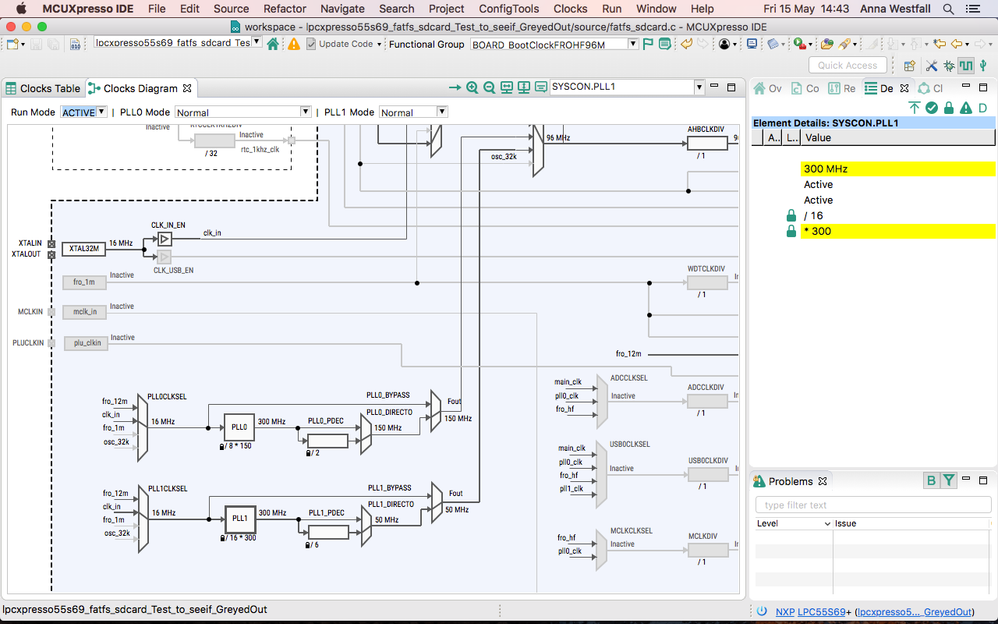

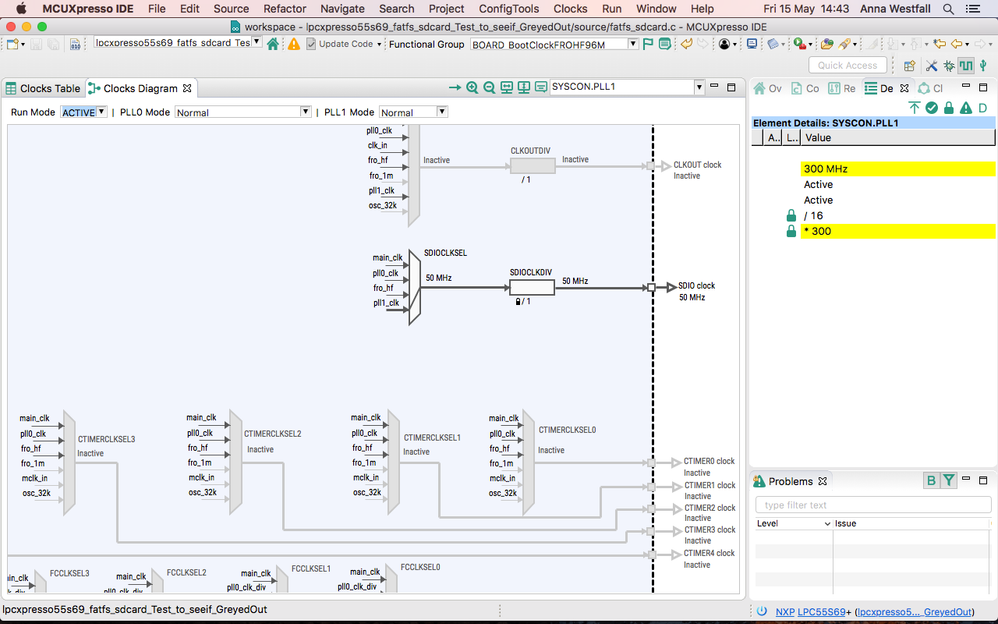

I am trying to use the inbuilt Clocks tool within MCUXpresso to configure the clocks for the FROHF96 functional group, for the LPC55S69EVK board. I want to use PLL1 with the SD card, so I can run this block at 50MHz (as opposed to using the FROHF96MHz clock, which will only allow me a maximum speed of 48MHz). I do not want to use PLL0 as this is already tied up running an I2S dma block.

If I configure PLL0 in the clocks tool, to use the XTAL32M clock running at 16MHz, and multiply and divide this to produce a 150MHz output, and then feed this to the SDIO block, and divide it by 3 to generate a 50MHz clock on the SDIO input, this configuration works.

If, however, I configure the PLL1 block in EXACTLY the same way, connect THIS to the SDIO block, and update the code accordingly, the frequency I read back from the sd block is 0Hz, and the sd card no longer properly functions. (See photo below for set-up within the MCUXpresso clocks tool).

Additionally, I cannot set up the multiplier of either PLL exactly how I would like for other purposes; if for example, I wanted to boost the sdio speed to 52MHz, I would need to activate the 1MHz FRO, connect this to whichever PLL, and then multiply by 52 in the PLL...however, whenever I try changing this multiplier number to 52, the software crashes.

Any help much appreciated.

Cheers

Rory

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Rory

Thanks for your reply.

I have tested your problems on the LPCXpresso55S69-evk, use lpcxpresso55s69_sdcard_fatfs demo from SDK_2.7.1 for LPCXpresso55s69. I use PLL1 to configure the SDIO clock in the clock config tool, and then download the updated code into the EVK ,it could not work normally.

Then, I checked the demo code in the SDK. and i found there is a bug in the lpcxpresso55s69_sdcard_fatfs demo from SDK_2.7.1 for LPCXpresso55s69 . As the figure below shows, there is a mistake in the CLOCK_Set PLL1Freq() function, it should be s_Pll1_Freq = pSetup->pllRate , not s_Pll0_Freq = pSetup->pllRate. This bug may cause the PLL1 clock couldn't work normally. When i fixed this bug, the SDIO can work with PLL1 normally.

Also, i' ve tested the PLL1 clock from the CLKOUT pin, it can output normally. And i checked the user manual, there is no remark about PLL1.

Finally, if you use the SDK code, please check your code to confirm that the CLOCK_Set PLL1Freq() function is right.

Hope it can help you.

Best Regards,

Mingwei Wang

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Rory

Thanks for your reply.

I have tested your problems on the LPCXpresso55S69-evk, use lpcxpresso55s69_sdcard_fatfs demo from SDK_2.7.1 for LPCXpresso55s69. I use PLL1 to configure the SDIO clock in the clock config tool, and then download the updated code into the EVK ,it could not work normally.

Then, I checked the demo code in the SDK. and i found there is a bug in the lpcxpresso55s69_sdcard_fatfs demo from SDK_2.7.1 for LPCXpresso55s69 . As the figure below shows, there is a mistake in the CLOCK_Set PLL1Freq() function, it should be s_Pll1_Freq = pSetup->pllRate , not s_Pll0_Freq = pSetup->pllRate. This bug may cause the PLL1 clock couldn't work normally. When i fixed this bug, the SDIO can work with PLL1 normally.

Also, i' ve tested the PLL1 clock from the CLKOUT pin, it can output normally. And i checked the user manual, there is no remark about PLL1.

Finally, if you use the SDK code, please check your code to confirm that the CLOCK_Set PLL1Freq() function is right.

Hope it can help you.

Best Regards,

Mingwei Wang

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mingwei,

thanks very much for looking into this for me. I made the correction in the "clock_SetPLL1Freq()" function like you said, and I now have this PLL running fine, which is fantastic. Can I assume that this bug in the SDK will be fixed in the next release (so as others don't experience this issue too!)

Cheers,

Rory

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, we will request it to be fixed in next release.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Your screenshot is blur. I can't know your clock setting with it.

Can you switch your PLL1 output to CLKOUT pin to check if your PLL1 output is as expectation?

Jun Zhang

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Zhang Jennie, I have had a further issue with PLL1. If PLL1 is enabled, yet is not connected to anything, my I2S output (which is connected to PLL0), runs slower, including the sound data I am sending via I2S DMA. To my mind there is evidently an issue with PLL1, perhaps it causes some interference to the rest of the chip.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jun Zhang -

Sorry about the low resolution of the image. I have reuploaded 2 different screenshots to substitue for my previous one original. See below:

I route PLL1 to the CLKOUT pin, and will test to see if it works. However, in the meantime, is there any issue known with this logic element (i.e. PLL1) on the LPC55S59 chip? i have used microchip parts before on which certain peripherals, say, the ADC, did not function at all!

Cheers

Rory

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jun Zhang - unfortunately I have remembered that the software for my picoscope does not run properly on MAC (as they only have a horribly unstable beta version), so it is unlikely I will be able to test this clkout pin. Again, see my previous reply for the new screenshots. Any help with diagnosing why PLL1 will not function is greatly appreciated. Cheers, Rory