- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- MCUXpresso Software and Tools

- :

- MCUXpresso General

- :

- Re: How to control UART0 with no printf or semiHosting

How to control UART0 with no printf or semiHosting

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to control UART0 with no printf or semiHosting

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Regarding UART0 and how to control it in MCUXpresso IDE

Using MKE04, and both UART0 and UART1, UART1 is working but can't control UART0.

Preprocessor:

__REDLIB__

SDK_OS_BAREMETAL

FSL_RTOS_BM

SDK_DEBUGCONSOLE=0

CR_INTEGER_PRINTF

PRINTF_FLOAT_ENABLE=0

CPU_MKE04Z64VLD4

CPU_MKE04Z64VLD4_cm0plus

__MCUXPRESSO

__USE_CMSIS

DEBUG

I have attached a screendump from the project.

Any sugesstions ?

/Claes

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi claes

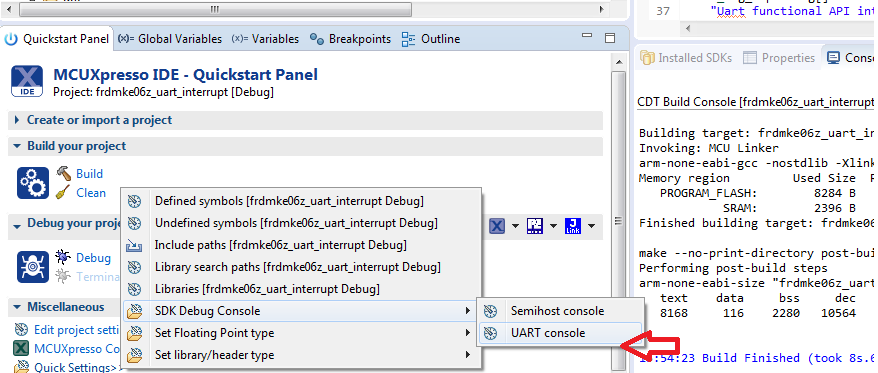

If you do not need printf or semihosting, please change the SDK debug console from semihost console to UART console.

Quick settings -> SDK Debug Console -> UART console

Have a great day,

Daniel

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Daniel,

From what I can see now the situation is like this:

using redlib(none), initiating UART0 and UART1, I can control UART1 , regarding

UART0 I can read a char from UART0->D, but I can't send anything on Tx, I have checked that Tx and Rx are active.

/* UART0&1 init */

SIM->SCGC |= SIM_SCGC_UART0_MASK;

SIM->SCGC |= SIM_SCGC_UART1_MASK;

uart_config_t uart_config;

uart_config.baudRate_Bps = 19200U;

uart_config.parityMode = kUART_ParityDisabled;

uart_config.stopBitCount = kUART_OneStopBit;

uart_config.enableRx = true;

uart_config.enableTx = true;

UART_Init(UART0, &uart_config, 20000000U);

UART_Init(UART1, &uart_config, 20000000U);

When compiling for release I use None (-O0) and debug level(none) etc.......

When I simply changed through "quick setting" and UART Consol, the code size just increased but still same problem with UART0

From the pin_mux.c you can see

/* pin 23,24 is configured as UART0_TX, UART0_RX */

PORT_SetPinSelect(kPORT_UART0, kPORT_UART0_RXPTB0_TXPTB1);

/* pin 36,37 is configured as UART1_TX, UART1_RX */

PORT_SetPinSelect(kPORT_UART1, kPORT_UART1_RXPTC7_TXPTC6);

/* pin 43 is configured as RESET_b */

PORT_SetPinSelect(kPORT_RESET, kPORT_RST_RSTPE);

/* pin 44,42 is configured as SWD_DIO, SWD_CLK */

PORT_SetPinSelect(kPORT_SWDE, kPORT_SWDE_SWDE);

SIM->SOPT0 = ((SIM->SOPT0 &

/* Mask bits to zero which are setting */

(~(SIM_SOPT0_RXDFE_MASK | SIM_SOPT0_CLKOE_MASK)))

/* UART0 RxD Filter Select: 0x00u. */

| SIM_SOPT0_RXDFE(0x00u)

/* Bus Clock Output Enable: 0x00u. */

| SIM_SOPT0_CLKOE(0x00u));

Any other Ideas ??

Regards

Claes

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI Claes

I would suggest you refer to below link for information about printing with semihosting and printing with UART terminal

https://community.nxp.com/docs/DOC-334074

Regards

Daniel