- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- MCUXpressoソフトウェアとツール

- :

- MCUXpressoコンフィグツール

- :

- Re: USB PLL setup values do not match

USB PLL setup values do not match

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

After using the clock config tool on OM13098 dev board (LPC546xx), I got the following values for USB PLL.

/*!< Set up USB PLL */

const usb_pll_setup_t usb_pllSetup = {

.msel = 15U,

.nsel = 0U,

.psel = 0U,

.direct = false,

.bypass = false,

.fbsel = false,

.inputRate = 12000000U,

};

CLOCK_SetUsbPLLFreq(&usb_pllSetup); /*!< Configure PLL to the desired value */

I expected these values to match the ones in CLOCK_EnableUsbhs0HostClock() in fsl_clock.c but they don't. Here are the values from CLOCK_EnableUsbhs0HostClock():

usb_pll_setup_t pll_setup = { 0x3FU, 0x01U, 0x03U, false, false, false, 12000000U };

CLOCK_SetUsbPLLFreq(&pll_setup);

Can I trust the values from the clock config tool? Is there a reason to use USB_N_DIV of 4 and USB_M_MULT of 64 in CLOCK_EnableUsbhs0HostClock()? Any advice would be greatly appreciated.

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Rex Lam,

Thanks for your reply.

It's Okay to select a different set of Pre-divider, Feedback-divider and Post-diver to output 48 or 96 MHz, the usb_pll_setup_t pll_setup = { 0x3FU, 0x01U, 0x03U, false, false, false, 12000000U }; just is a template.

Hope this is clear.

Have a great day,

TIC

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I noted the same discrepancy between the clock config tool and the source in fsl_clock.c.

Although both sets of figures may arrive at the same output clock frequency, the concern I have is that the settings in fsl_clock.c appear to set the USB PLL beyond the recommended MAX frequency in the datasheet.

So I'd like to know if it is safe to use the fsl_clock.c setting function, or do I have to implement my own copy using the values from the clock config tool?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

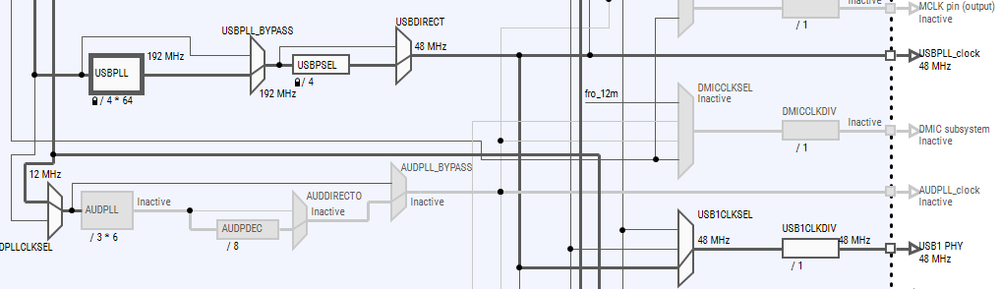

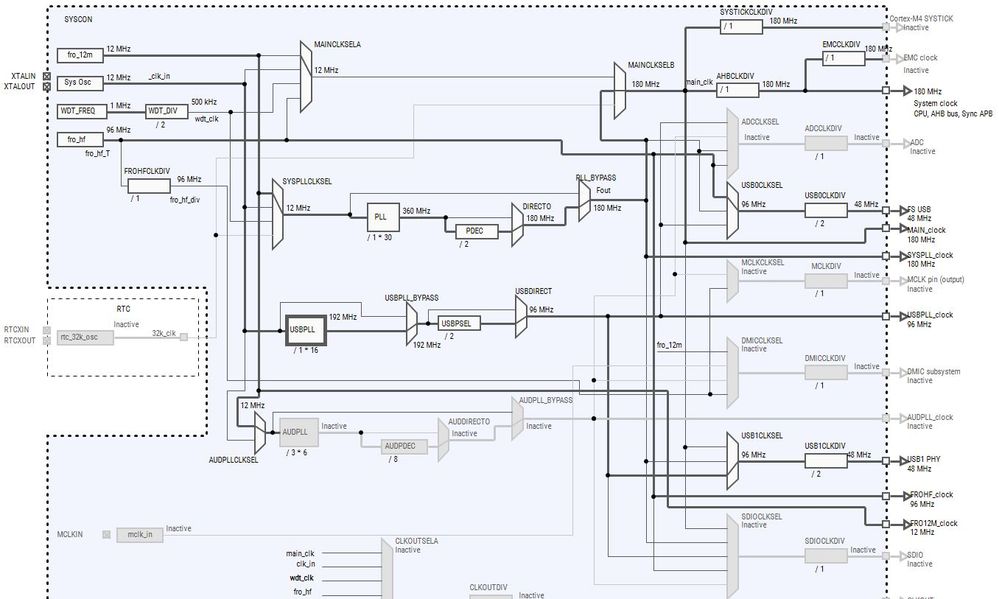

Based on the formula Fout = M*(Fin/N)/(2*P), the USB PLL is not set beyond the recommended MAX frequency (using the values in fsl_clock.c). This is what it looks like in the clock tool.

So it should be safe to use fsl_clock.c functions.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Okay, yes I see that I missed the fact that the order of the psel and nsel figures is different in the auto generated code.

Thanks

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Rex Lam,

Thank you for your interest in NXP Semiconductor products and for the opportunity to serve you.

According the formula, Fout = M*(Fin/N)/(2*P), Fcco = M * (Fin/N) , when usb_pll_setup_t pll_setup = { 0x3FU, 0x01U, 0x03U, false, false, false, 12000000U };,

it's easy to get USB clock = 64*(12 MHz/2)/(2*4)= 48 MHz.

About the structure usb_pllSetup that clock config tool generates, I can't jump to the conclusion that the structure is wrong before I can get more information, so I was wondering if you share the screenshot of the clock config tool.

Have a great day,

TIC

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Jeremy,

Thank you for your quick response. In usb_pll_setup_t, the second field is actually psel, and the third field nsel. Therefore, the formula is

64*(12 MHz/4)/(2*2) = 48 MHz

I have attached my clock diagram. I hope this is what you are asking for. I think the final frequencies are correct, but I would like to understand why it is different than the values used in fsl_clock.c.

Rex

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Rex Lam,

Thanks for your reply.

It's Okay to select a different set of Pre-divider, Feedback-divider and Post-diver to output 48 or 96 MHz, the usb_pll_setup_t pll_setup = { 0x3FU, 0x01U, 0x03U, false, false, false, 12000000U }; just is a template.

Hope this is clear.

Have a great day,

TIC

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you Jeremy. Much appreciated.