- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- QorIQ Processing Platforms

- :

- Layerscape

- :

- Re: LS1046ARDB DDR initialization error with Target Initialization File

LS1046ARDB DDR initialization error with Target Initialization File

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

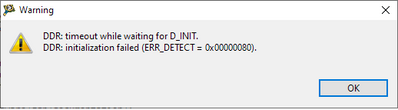

Hi all,

I am starting to use LS1046RDB. Most of CodeWarrior functionalities work well but I get the following error message when connecting with the LS1046A_RDB Target Connection.

I believe that the whole DDR configuration is performed with the Target Initialzation File, but I may be missing something.

Thanks in advance

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

DDR controller configuration parameters should be changed.

In Target Connections panel, please double click "LS1046A_RDB(1)", the click "Target Initialization File" panel, you need to modify "DDR Initialization" section in this fie.

Do you have u-boot running on the target board?

If yes, you could create a QCVS DDRC project, and select "From Target" Configuration mode in DDR configuration panel. After create the project, please refer to DDR controller configuration parameters in ddrCtrl_1.py under Generated_Code to modify "Target Initialization File".

If there is no u-boot running on the target board, you could apply the attached patch to packages/firmware/atf/, then build SD firmware with command "flex-builder -i mkfw -m ls1046ardb -b sd" in LSDK 20.12 build environment and deploy it to SD card to boot the target board.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It seems that there is DDR controller initialization problem on your target board.

Please use the latest CodeWarrior for ARMV8 CW4NET v2020.06, please download the installation file from https://drive.google.com/file/d/1Kjq1nLYrtIfWAHYrup5Cf-TTEJI9iWiu/view?usp=sharing ,

Please download the patch release from https://drive.google.com/file/d/1g4FbibmVuEWQdEhCuaOqMUvs6_xQzzYC/view?usp=sharing, install the patch release from Help->Install New Software->Add->Archive.

Please check whether UDIMM 18ASF1G72AZ-2G3B1 is integrated on your target board.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your reply.

I had already installed the program and patch you mentioned. However, the UDIMM is different from the one you mentioned: it is MTA18ADF2G72AZ-2G6E1ZG. Should the configuration commands change?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

DDR controller configuration parameters should be changed.

In Target Connections panel, please double click "LS1046A_RDB(1)", the click "Target Initialization File" panel, you need to modify "DDR Initialization" section in this fie.

Do you have u-boot running on the target board?

If yes, you could create a QCVS DDRC project, and select "From Target" Configuration mode in DDR configuration panel. After create the project, please refer to DDR controller configuration parameters in ddrCtrl_1.py under Generated_Code to modify "Target Initialization File".

If there is no u-boot running on the target board, you could apply the attached patch to packages/firmware/atf/, then build SD firmware with command "flex-builder -i mkfw -m ls1046ardb -b sd" in LSDK 20.12 build environment and deploy it to SD card to boot the target board.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi again yipingwang,

Thank you for all the help.

I am trying to use ddrCtrl_1.py generated by QCVS as you suggested. I have copied its contents into my Target Initialization File. However, a new problem has arised: the new initialization does not exit the while loop in A009803_Erratum(). I am copying its contents below:

def A009803_Erratum():

DDR_BASE = 0x01080000

# 1. Configure the DDR registers as normal with parity enabled

CCSR_BE_M(0x01080114, 0x00401070 | 0x00000020)

# 2. Set ERR_DISABLE[APED]

CCSR_BE_M(0x01080E44, 0x00 | 0x00000100)

# 3. Set DDR_SDRAM_CFG[MEM_EN]

CCSR_BE_M(0x01080110, 0x65200000 | 0x80000000)

# 4. Poll for DEBUG_2[30] to be set

while True:

time.sleep(0.2)

debug_2_value = CCSR_BE_D(DDR_BASE + 0xF04)

if debug_2_value & 0x2 != 0:

break

# 5. Clear ERR_DIS[APED]. Parity checking is now enabled

CCSR_BE_M(0x01080E44, 0x00 & (0xFFFFFFFF ^ 0x00000100))

I understand that it is waiting for a certain value at register 0x1080F04. I have checked with UART writes at that point an the value is kept at 0x2100. I have also looked into LS146ARM but that address is not described in the manual. Should I skip that while loop?

Best regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In the original CW initialization file, I didn't find A009803_Erratum was applied, please ignore it

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi again yipingwang,

It seems I made some mistake when gerating the Python code after reading the configuration from the target. I have done this again and it worked.

Thank you for your help!