- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- QorIQ Processing Platforms

- :

- Layerscape

- :

- Re: LS1046A IFC Async NAND interface

LS1046A IFC Async NAND interface

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LS1046A IFC Async NAND interface

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, I'm looking for an explanation for the base address of NAND being used in u-boot for both the RDB and FRWY development boards. The base address is 0x7e800000, and I can't seem to figure out why this is the case.

If I added an additional NAND chip, using CS1 instead of CS0, would I increase this size by the size of the chip?

Would I use the same address?

How was this address derived?

Any pointers are greatly appreciated. Thank you in advance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

SUPER IMPORTANT POINT ABOUT THIS INTERFACE...

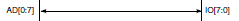

The bus between the NAND chip and the LS1046A IFC is bitwise reversed... Yes, AD0 connects to AD7 on your NAND part, AD1 to AD6, and so on... In the 2500+ page reference manual, there are actually 3 places that describe this bitwise reversal, and they are in picture form, not words.

(see figures 22-58, 22-59, and 22-60) It looks like this:

Something you could easily over look, because lets face it; when I think about connecting address and data busses, I go with 0 goes to 0, 1 goes to 1, etc...

I'm thinking this was a mistake originally; wonder what the first edition of the reference manual looks like.

Anyway, be careful, or you'll find yourself trying to flip bits in software or respinning your board to get things to work correctly...

-Dave

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This happens in multiple other places as well. E.g. SerDes lane A is RX3/TX3, lane D is RX0/TX0. The registers are numbered incorrectly too. That is, they are numbered from bit 0 to 31, but bit 0 is what you get by doing 1 << 31... This is not due to byte-swapping either, since if you e.g. read a big-endian register with a little-endian read (byte swapped) the bits (as documented) go 24 .. 31, 16 .. 23, 8..15, 0..7 (instead of 7..0, 15..8, 23..16, 31..24 like usual). I think whoever wrote the manual just loved naming the most-significant bit 0 instead of the least-significant bit.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ha... yes the ordering within registers confused me as well originally, but it became apparent that the first bit reading left to right that was labeled bit0 was actually the MSb... I adjusted my thinking while reading the reference manual after that...

But more specifically, what I was referring to was the actual bus between the IFC and the NAND part, and that the reference manual shows the bitwise reversal in picture form. There is nothing written with words that indicates the actual bus interface must be bitwise flipped. On my first spin of the board, I connected b0 from the LS1046A to b0 on the NAND chip, and b1-b1, and so on... This is exactly backwards. On the second spin of my board, I connected b0 from the LS1046A to b7 on the NAND chip, b1->b6, b2->b5, and so on, and it works correctly...

This is what I was referring to... Still an important note for others.

-Dave

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Hector, I've done a bit more reading and experimenting by modifying the base address on a couple of chips on my custom board, and I think I understand the solution now, namely: The address doesn't mean a thing...

Regarding SRAM buffer for NAND devices

see section 22.5.5 SRAM buffer of the LS1046A Reference Manual, Rev. 3, 08/2021

- Buffer RAM consists of 16KB (16,384 bytes) or 0x4000 bytes

- This RAM is shared as read/write memory for ALL devices (since they can’t be accessed at the same time)

- The base address for the device is simply a way to differentiate them from each other, however address spacing must account for the buffer size, since it is shared and merely remapped for each device.

- Base address of 0x7E800000 is arbitrary

U-boot software works with NAND1 and NAND2 base addresses set as follows:

#define CONFIG_SYS_NAND_BASE 0x60000000

#define CONFIG_SYS_NAND_BASE2 0x60004000What are your thoughts?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ok, this address refers to the SRAM buffer being used by the IFC when you're talking to NAND. It has a maximum size (I think it's 0x10000), and since the buffer (which is memory mapped I believe also) is used for all NAND devices (you can't access more than one at a time), the address is the same for all...

I still haven't figured out where the address came from... although, I have come to realize the reference manual is pretty big

Still looking for help understanding how this address is known...

Anyone?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Daves Garage,

This post is to inform you that I'm working on your case,

Kindly give some time and I will update you,

I'll keep you informed of the progress.

Best Regards,

Hector Villarruel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Well, this is officially the longest I've ever waited for a response from NXP (1.5 years to date so far)... Hoping still for a response to my original question... before the processor goes EOL anyway.