- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- QorIQ Processing Platforms

- :

- Layerscape

- :

- LS1043a clock configuration issue?

LS1043a clock configuration issue?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Platform: LS1043a target board

LSDK: lsdk2012

QSPI FLASH: S25FS512SDSMFI011

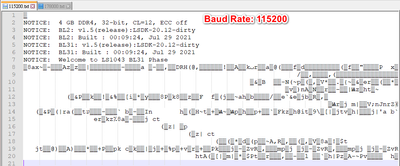

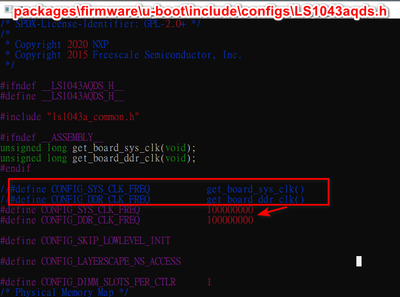

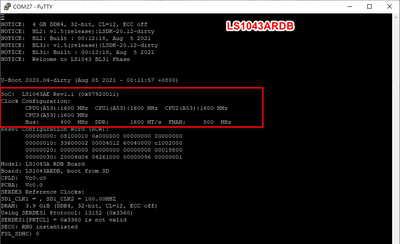

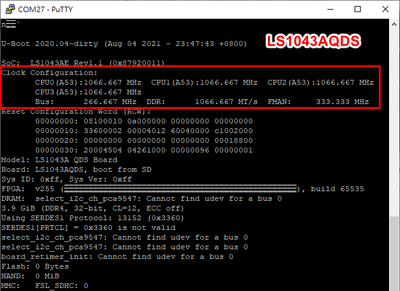

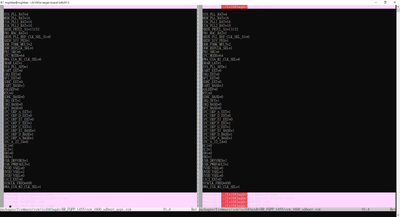

I generated the SD boot with the LSDK version lsdk2012, but the figure 1 below shows the baud rate was changed when it ran to BL31. The baud rate is correctly output at 115200 before BL31, then I measured the waveform it became 178000 after BL31. The figure 2 below shows the clock configuration data is incorrect.(The correct clock configuration is figure 3.) Is there anything I can modify?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I found the root cause.

In the config setting of LS1043aQDS CONFIG_SYS_CLK_FREQ and CONFIG_DDR_CLK are obtained by using get_board_sys_clk() and get_board_ddr_clk().

LS1043aRDB sets the value directly at 100M.

After correcting this part in LS1043aQDS, the clock configuration is correct.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In atf source code, please define the following in plat/nxp/soc-ls1043/ls1043aqds/platform_def.h

/* UART related definition */

#define NXP_CONSOLE_ADDR NXP_UART_ADDR

#define NXP_CONSOLE_BAUDRATE 115200

In u-boot source, please define the following in include/configs/ls1043a_common.h.

#define CONFIG_SYS_NS16550_CLK (get_serial_clock())

Modify to

#define CONFIG_SYS_NS16550_CLK 115200

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

After I modified as you suggested, the baud rate value measured became to around 12M and it's over UART spec to output data.

Then I modified “#define CONFIG_SYS_NS16550_CLK 115200” to “#define CONFIG_SYS_NS16550_CLK (get_serial_clock())” , the baud rate retrieved 178000.

I think the root cause is the core frequency is changed from 1600MHz to 1066MHz to affect the baud rate.

How to correct the core frequency to 1600MHz?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please customize RCW configuration file packages/firmware/rcw/ls1043aqds/RR_FQPP_1455/rcw_1600_sdboot_qspi.rcw according to your custom board.

Is Sys Clock 100 MHz on your custom board?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, system clock is 100MHz on custom board.

BTW, I tested with the same custom RCW and DDR value based on LS1043ardb, the test result below shows the clock configuration is correct, but not for LS1043adqs.

Is there any difference between ls1043aqds and ls1043ardb on clock configuration?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please run the following command to get the difference.

vimdiff packages/firmware/rcw/ls1043aqds/RR_FQPP_1455/rcw_1600_sdboot_qspi.rcw packages/firmware/rcw/ls1043ardb/RR_FQPP_1455/rcw_1600_sdboot.rcw

rcw_1600_sdboot_qspi.rcw enables QSPI in SD boot.

rcw_1600_sdboot.rcw enables IFC in SD boot.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The result below shows no difference.

Is it a bug for LS1043aqds on clock configuration? If yes, how to correct it?

.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I currently tested on our custom board, so I should use custom RCW file rather than LS1043aQDS. It's weird that I generated the SDboot image with the same custom RCW file based on LS1043aRDB in LSDK2012 and LS1043aQDS in LSDK2012 separately. After SDboot on our custom board, I found the SDboot file by using LS1043aRDB in LSDK2012 generated works correctly, but not for LS1043aQDS in LSDK2012.

Apart from the RCW/DDR file, I didn't modify anything. Why the SDboot file generated from the LS1043aQDS in LSDK2012 works incorrectly?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I found the root cause.

In the config setting of LS1043aQDS CONFIG_SYS_CLK_FREQ and CONFIG_DDR_CLK are obtained by using get_board_sys_clk() and get_board_ddr_clk().

LS1043aRDB sets the value directly at 100M.

After correcting this part in LS1043aQDS, the clock configuration is correct.