- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- QorIQ Processing Platforms

- :

- Layerscape

- :

- LS1020A RTC questions

LS1020A RTC questions

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LS1020A RTC questions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Just finding my way around the documentation for the LS1020A but cannot seem to find anything about the RTC (real-time clock) capability (or lack of it). Is there an RTC on chip that just requires an external battery, or what is the device type I need to connect to pin TA_BB_RTC?

1) On what pin should I provide my 32768Hz clock for the LS1020A, is it TA_BB_RTC?

2) At what voltage levels?

3) Which pin is the battery voltage supplied on, is it TA_BB_VDD?

4) What is the current draw from the battery pin.

I am not using the trust/SecMon feature if that question comes up.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1) The TA_BB_RTC or RTC pins can be used as clock source for the LS1021A RTC. See the Figure 4-8 of the LS1021A Reference Manual:

2) Recommended value is 1.8V. See the Table 3 of the LS1021A Datasheet:

3) Yes, the TA_BB_VDD pins is power supply pin for the TA_BB_RTC pin. See the Table 1 of the LS1021 Datasheet. Find the TA_BB_RTC pin and power supply for this pin.

The OVDD is power supply for the RTC/GPIO1_14 pin.

4) See the Table 6 of the LS1021A Datasheet.

Have a great day,

Pavel

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Pavel,

I have the following follow up questions. Please help answer these. In advance, thank you.

1) App note AN5097 states:

• Bit-swap is only allowed within a nibble.

• Bit-swap across two nibbles is not allowed.

Does this note refer to just x4 memory configurations (where there is one DQS pair per 4-bits)? Or does it also refer to x8 configurations (where there is one DQS pair per 8-bits)?

2) In app note AN5097 it states "17 For QorIQ products with DDR3L and DDR4 memory options, there is an external VREF pin available for DDR3L mode. When DDR4 mode is used the external VREF pin needs to be grounded."

To which pin is it referring as I don't see an equivalent comment in the reference manual?

3) In an earlier email it was suggested that the TA_BB_RTC be driven from a 1.8V device. However, I am using TA_BB_RTC as my clock input which is powered from TA_BB_VDD (which is a 1V supply), surely the I/O voltage to that pin should be a maximum of 1V? Or is the pin tolerant to a higher voltage? Where in the datasheet does it show the recommended maximum voltage driving pin R6?

4) It looks to me like there is an inconsistency in the datasheet.

Page 20 says MDC/MDIO are related to L1VDD.

Page 61 says that Ethernet Management Interface is powered by LVDD.

Page 92 says that the MDC/MDIO pins are available on LVDD and L1VDD.

Could you clarify which comment is correct, and perhaps get the datasheet corrected.

5) It looks to me like there is another inconsistency in the datasheet.

Page 51 says DVDD is 1.8 V ± 90 mV

The schematics for LS1021A-IOT and TWR-LS1021A-PB both have DVDD connected to 3.3V I/O.

Pin J2 is a good example.

Could you tell me the real voltage range for DVDD.

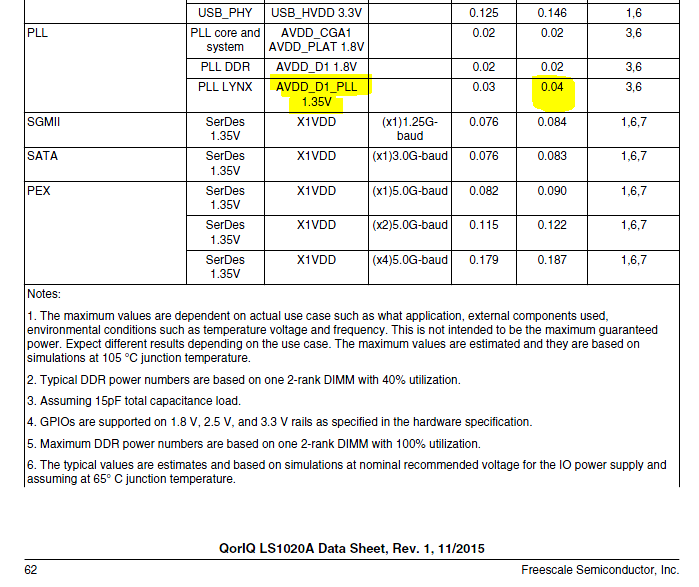

6) Could you please confirm that the power draw highlighted in yellow in the attached is the total power drawn by both the AVDD_SD1_PLL1/2 pins, and not per PLL pin.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- 1. It is information from the JEDEC Standard No. 21C:

- 2. In DDR4, VREF is only used for address/command bus of DDR4 DRAM. Memory controller VREF is generated internally. When DDR4 mode is used the external VREF pin needs to be grounded. It is D1_MVREF pin of the LS1021A.

- 3. The TA_BB_RTC pin recommended voltage level is 1V see the Table 3 of the LS1021A Datasheet.

- 4. See Note 7 for the Table 3 of the LS1021A Datasheet:

LVDD and L1VDD must always be the same voltage.

- 5. Find the DVDD_VSEL (435-436 bits) of the LS1021A RCW. See the Table 4-14 of the LS1021A Reference Manual. These bits determinates internal switch for using external DVDD voltage. If DVDD_VSEL is set to 0b10, external DVDD powers supply can be 3.3V.

If DVDD_VSEL is set to 0b00, external DVDD powers supply should be 1.8V. Do not use 3.3V DVDD if DVDD_VSEL is set to 0b00. The LS1021a can be damaged.

- 6. It is power consumption of PLL. It is not current from PLL pins.

Have a great day,

Pavel

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------