- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- QorIQ处理平台

- :

- Layerscape

- :

- Re: DPAA2 qDMA

DPAA2 qDMA

Hello,

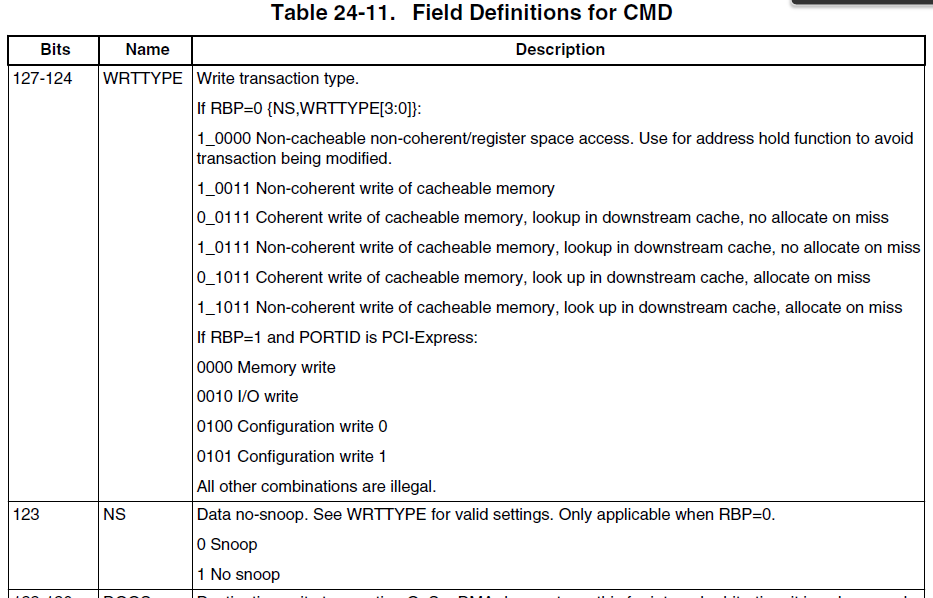

Below is the CMD field definition of qDMA Destination&Source Descriptor Format:

I wonder if the configuration 1_0000(Non-cacheable non-coherent/register space access ) is supported on LX2160.

My case is to copy one cache-off memory to another cache-off memory through qDMA.

If I use 0_1011 configuration, I have to use cache invalidate and cache flush operation after every qDMA copy, otherwise I cannot get the correct data.

When I set the CMD field to 1_0000, there are always errors with FD.Whether lx2160 supports configuration 1_0000 (Non-cacheable non-coherent/register space access)?

已解决! 转到解答。

Please refer to the feedback from the application team.

OK, I see now what is the required test. The customer thinks qDMA descriptor field WRTTYPE is the only knob that controls coherency in the SoC. In fact the SMMU setting is also a factor in this issue. This is because qDMA requests goes through SMMU and get translated and based on the target page coherency settings the CCN508 will act accordingly. In the customer example , he mentioned the need to do cache flush first, this means that if he did not do that the qDMA will move data from DDR and not cache, this tells you that snooping action did not happen. Also when the customer says that there is a need to invalidate the cache after transfer is done, this tells you that the transfer was done to DDR without snooping being activated for core caches to be updated thus he needed to invalidate the core caches so as to force the loads to read DDR correctly.

My recommendation is that the customer focus on the SMMU/TLB settings for the pages that he is using for qDMA transactions and make sure that these pages have proper coherency /cache settings.

Best Regards,

Hello,

Any update?

When I use configuration 1_0000(Non-cacheable non-coherent/register space access ), there are always interrupt with FD error.

When I use configuration 0_1011 (Coherent write of cacheable memory, look up in downstream cache, allocate on miss ),

if I don't invoke cache flush operation after qDMA copy operation I can't get the correct data. I think this is because memory is cacheable attribute.

I want to use th LX2160 DPAA2 qDMA to copy data without cache flush operation. How can I configure it, or what else has been ignored?

Thanks and Best Regards,

Minghu

Hi Yiping,

Thanks for your reply!

I tried 1_0011 and all other configuration combinations, the result is I must invoke cache-flush operation on the source memory address before qDMA copy, and cache-invalidate on the destination address after qDMA copy, otherwise the data in destination memory space is not correct.

Any suggestions?

Thanks and Best Regards,

Minghu

Please refer to the feedback from the application team.

OK, I see now what is the required test. The customer thinks qDMA descriptor field WRTTYPE is the only knob that controls coherency in the SoC. In fact the SMMU setting is also a factor in this issue. This is because qDMA requests goes through SMMU and get translated and based on the target page coherency settings the CCN508 will act accordingly. In the customer example , he mentioned the need to do cache flush first, this means that if he did not do that the qDMA will move data from DDR and not cache, this tells you that snooping action did not happen. Also when the customer says that there is a need to invalidate the cache after transfer is done, this tells you that the transfer was done to DDR without snooping being activated for core caches to be updated thus he needed to invalidate the core caches so as to force the loads to read DDR correctly.

My recommendation is that the customer focus on the SMMU/TLB settings for the pages that he is using for qDMA transactions and make sure that these pages have proper coherency /cache settings.

Best Regards,

Hello minghu.du@windriver.com,

Unfortunately we only handle questions regarding MATLAB/Simulink and our toolboxes - I would recommend you post your question on the Layerscape community.

Kind regards,

Razvan.