- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- QorIQ Processing Platforms

- :

- Layerscape

- :

- Re: DDR read/write issues custom board LS1046A

DDR read/write issues custom board LS1046A

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

DDR read/write issues custom board LS1046A

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all,

I am in the process of trying to bring up a LS1046A board. Its a custom board based heavily off the Freeway design. The first step I am trying to do is get the connection diagnostics to pass with RCW override and DDR settings. D_INIT is cleared and its gets to the DDR memory access test. However when checking logs I can see that the DDR values do not match their expected values. See picture and logs(Read_Write_mem.txt). I see some resemblance of the expected values. D_Init_value is set to 0xDEADBEEF.

Some things we tried and validated:

Hardware:

- Schematics reviewed and double checked

- Voltages are checked. GVDD, VREF, VTT and VPP

- Input and output DDR clocks

- DRAM reset signal is correct

- MEM enable signal is correct

Software:

- RCW correct and double checked. See below

- DQS skews are correct and double checked with schematics

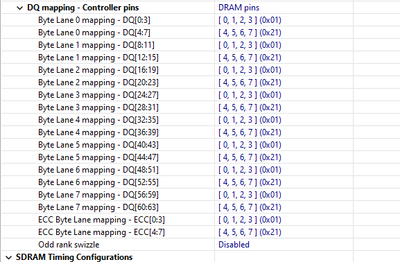

- DQ mapping should be correct. Using the exact same layout as the Freeway board. See attached.

I am unable to find a DDR config for the Freeway board. Is this something we can get to compare to our settings? Any pointers to what might be wrong? Im assuming its settings related since D_INIT is cleared and we are actually able to read/write to DDR.

You can also find the logs below for the test for centering the clocks. Its ran with RCW override with the RCW mentioned below. CCS Output is also added.

RCW:

RCWSR1:0x0810000d

RCWSR2:0x0a000000

RCWSR3:0x00000000

RCWSR4:0x00000000

RCWSR5:0x00000000

RCWSR6:0x40000002

RCWSR7:0x40000000

RCWSR8:0xc1000000

RCWSR9:0x00000000

RCWSR10:0x00000000

RCWSR11:0x00000000

RCWSR12:0x00000800

RCWSR13:0x00000000

RCWSR14:0x00000000

RCWSR15:0x00000096

RCWSR16:0x00000001

Any tips and/or pointers to potential fixes is appreciated.

Rinke

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please refer to the following procedure to use QCVS DDRv tool to do DDR validation and optimization.

1. QCVS DDRv tool doesn't support RCW overriding function, you need to program RCW binary image to QSPI flash and configure the target board to boot from QSPI flash.

Please refer to section "8.6 Board Recovery" in C:\Freescale\CW4NET_v2020.06\CW_ARMv8\ARMv8\Help\PDF\ARMv8_Targeting_Manual.pdf to program RCW to QSPI NOR flash.

In your description, your RCW configuration is incorrect. In your configuration, RCW[10-15] is 010000 (16:1), so DDR data rate is 1600MT/s, however you configure DDR data rate as 2100MT/s in QCVS DDRv project.

Please use the following method to build RCW binary image in your Linux host PC.

$ git clone https://github.com/nxp-qoriq/rcw.git

$ cd rcw

Then modify ls1046afrwy/NN_NNQNNPNP_3040_0506/rcw_1600_qspiboot.rcw according to your target board.

$ make

You will get ls1046afrwy/NN_NNQNNPNP_3040_0506/rcw_1600_qspiboot.bin, please program it to the beginning of your QSPI NOR flash.

2. Please refer to the attached DDR controller registers configuration file, which I read from LS1046AFRWY target board.

When creating a QCVS DDR project, in DDR configuration panel, please select configuration mode as "From memory file" and "Discrete DRAM" and specify the input file as the attached CodeWarrior Register Text file.

3. Please double click "DDR_mc1:DDR" to open Properties panel, please modify parameters in Properties panel according to your DDR datasheet and the schematics of your target board.

4. In the validation panel, please check all Validation stage and Operational DDR tests to connect to your target board to finish all the validations.

5. Please save the configuration and generate the latest code files from Project->Generate Processor Expert code. In "Generated_Code" folder, please use "ddr_init1.c" in ATF source code atf/plat/nxp/soc-ls1046a/ls1046afrwy, please use "ddrCtrl_1.py" in CodeWarrior initialization file.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the DDR config of the Freeway board!

1. If DDRv tool does not support RCW overriding. What it this setting for?

Thanks for the find in the RCW. Found it aswell and changed it to 2100. Does not make a difference.

You point to ARMv8_Targeting_Manual.pdf section 8.6 for bringup of the board. This requires the flash manager to work. Flash manager requires the initialization file which requires DDR to function. So I first need to create a working DDR config before I can flash RCW right?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The flash programmer is configured to use OCRAM(rather than DDR) in CodeWarrior, you could use CodeWarrior to program RCW to QSPI flash first.

Please refer to the following RCW configuration on LS1046AFRWY

Reset Configuration Word (RCW):

00000000: 0c150010 0e000000 00000000 00000000

00000010: 30400506 00800012 40025000 c1000000

00000020: 00000000 00000000 00000000 00038800

00000030: 20044100 24003101 00000096 00000001

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the answer. Im trying to first flash the RCW into QSPI now. The flash manager indicates its able to correctly flash. Which is nice.

The RCW im trying to write is attached.

I am specifically not turning on any Serdes configurations to avoid issues with it.

Now im trying to run the DDRv tool without RCW override. Then I get the following error:

#################### Result for: wrlvl_searcher ###### Run 1 ######################################

Test result: [

============================================================

Updated: WRLVL_CNTL = 0x86750605, WRLVL_CNTL_2 = 0x00000000, WRLVL_CNTL_3 = 0x00000000, SDRAM_CLK_CNTL = 0x02800000

Traceback (most recent call last):

File "C:\Freescale\CW4NET_v2020.06\Common\QCVS\Optimization\resources\QorIQ\ARMv8/ddr/wrlvl_searcher.py", line 204, in write_leveling_start_searcher

debug = ddr_init.read_debug_regs(ddr_ctrl, session)

File "C:\Freescale\CW4NET_v2020.06\Common\QCVS\Optimization\resources\QorIQ\ARMv8\ddr\ddr_init.py", line 812, in read_debug_regs

swap = (ddr_ctrl['endianness'][default_space] == 'little_endian')

KeyError: 'endianness'

]

Any pointers what to look for?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Im also trying to run the initialization file without RCW override now. It was telling me to remove the RESET_REQ_B signal line from the reset cirquit to get a better error. After disconnecting I get this message. When I dump the contents of the QSPI memory I can see the contents of the RCW and preamble are all in the QSPI. Also when checking QSPI clock we can see a nice signal on boot being there. How do we solve this?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

For QSPI flash RCW, byte swap is required. However in the recent released SDK byte swap script is provide in ATF source code. Please refer to the following procedure to generate ATF pbl image.

$ git clone https://github.com/nxp-qoriq/atf.git

$ cd atf

$ git checkout -b LSDK-21.08 LSDK-21.08

$ sudo apt-get install gcc-aarch64-linux-gnu

$ export CROSS_COMPILE=aarch64-linux-gnu-

$ make PLAT=ls1046afrwy bl2 BOOT_MODE=qspi pbl RCW=~/data/rcw/ls1046afrwy/NN_NNQNNPNP_3040_0506/test.bin

Note: please specify RCW binary path generated by you.

You will get build/ls1046afrwy/release/bl2_qspi.pbl, please program bl2_qspi.pbl at offset 0 of QSPI flash.

Please refer to the attached image generate with your RCW text file.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the help!

Is the ATF the only thing I need on the QSPI memory to be able to run the DDRv tool? Or would I also need BL2 and/or BL31/33? Is there a full instruction list to run the DDRv tool?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

After programing bl2_qspi.pbl at offset 0 of QSPI flash, there is valid RCW on QSPI flash, then you could do DDRv validation. No need to deploy BL31/BL33 images.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

When flashing your exact file into QSPI nor flash and then running the ddrv tool I am still running into the endianness issue. Even when I build the pbl myself I have this issue.

#################### Result for: wrlvl_searcher ###### Run 1 ######################################

Test result: [

============================================================

Updated: WRLVL_CNTL = 0x86750605, WRLVL_CNTL_2 = 0x00000000, WRLVL_CNTL_3 = 0x00000000, SDRAM_CLK_CNTL = 0x02800000

Traceback (most recent call last):

File "C:\Freescale\CW4NET_v2020.06\Common\QCVS\Optimization\resources\QorIQ\ARMv8/ddr/wrlvl_searcher.py", line 204, in write_leveling_start_searcher

debug = ddr_init.read_debug_regs(ddr_ctrl, session)

File "C:\Freescale\CW4NET_v2020.06\Common\QCVS\Optimization\resources\QorIQ\ARMv8\ddr\ddr_init.py", line 812, in read_debug_regs

swap = (ddr_ctrl['endianness'][default_space] == 'little_endian')

KeyError: 'endianness'

]

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ive been trying some different RCW settings. I feel there were still some incorrect settings. This is my current RCW

RCWSR1:0x0c150010

RCWSR2:0x0e000000

RCWSR3:0x00000000

RCWSR4:0x00000000

RCWSR5:0x00000000

RCWSR6:0x00f00002

RCWSR7:0x40000000

RCWSR8:0xc1000000

RCWSR9:0x00000000

RCWSR10:0x00000000

RCWSR11:0x00000000

RCWSR12:0x00018800

RCWSR13:0x20024100

RCWSR14:0x00000000

RCWSR15:0x00000096

RCWSR16:0x00000001

When I put these settings into the RCW override function in the initialization file I can run the connection diagnostics tool and it will pas DDR initialization but then fail on read/write. Like i had before. I feel the issue is in getting this RCW on the board.

I am converting above into the format below for building it in the ATF.

/*

* LS1046AFRWY RCW for SerDes Protocol 0x3040_0x0506

*

* 4G configuration -- 4G QSGMII + 2 PCIe

*

* Frequencies:

*

* Sys Clock: 100 MHz

* DDR_Refclock: 100 MHz

*

* Core -- 1600 MHz (Mul 16)

* Platform -- 600 MHz (Mul 6)

* DDR -- 2100 MT/s (Mul 21)

* FMan -- 700 MHz (CGA2 /2)

* QSGMII -- 100 MHz (5G)

* PCIE -- 100 MHz (5G)

* eSDHC -- 1400 MHz (CGA2 /1)

*

* Hardware Accelerator Block Cluster Group A Mux Clock:

* FMan - HWA_CGA_M1_CLK_SEL = 6 - Async mode, CGA PLL 2 /2 is clock

* eSDHC, QSPI - HWA_CGA_M2_CLK_SEL = 1 - Async mode, CGA PLL 2 /1 is clock

*

* Serdes Lanes vs Slot information

* Serdes1 Lane 0 (D) - Unused

* Serdes1 Lane 1 (C) - Unused

* Serdes1 Lane 2 (B) - QSGMII6,QSGMII5,QSGMII10,QSGMII1 port

* Serdes1 Lane 3 (A) - Unused

*

* Serdes2 Lane 0 (A) - Unused

* Serdes2 Lane 1 (B) - PCIe2 Gen3 x1

* Serdes2 Lane 2 (C) - Unused

* Serdes2 Lane 3 (D) - PCIe3 Gen3 x1

*

* PLL mapping: 2222_2222

*

* Serdes 1:

* PLL mapping: 2222

*

* SRDS_PLL_REF_CLK_SEL_S1 : 0b'01

* SerDes 1, PLL1[160] : 0 - 100MHz for QSGMII

* SerDes 1, PLL2[161] : 1 - 100MHz for QSGMII

* SRDS_PLL_PD_S1 : 0b'0

* SerDes 1, PLL1 : 0 - not power down

* SerDes 1, PLL2 : 0 - not poewr down

* HWA_CGA_M1_CLK_SEL[224-226] : 6 - Cluster Group A PLL 2 /2 to FMan

*

* Serdes 2:

* PLL mapping: 2222

* SRDS_PLL_REF_CLK_SEL_S2 : 0b'00

* SerDes 2, PLL1[162] : 0 - 100MHz for PCIe

* SerDes 2, PLL2[163] : 0 - 100MHz for PCIe

* SRDS_PLL_PD_S2 : 0b'00

* SerDes 2, PLL1 : 0 - not power down

* SerDes 2, PLL2 : 0 - not poewr down

* SRDS_DIV_PEX_S2 : 0b'01

* 00 - train up to max rate of 8G

* 01 - train up to max rate of 5G

* 10 - train up to max rate of 2.5G

*

* DDR clock:

* DDR_REFCLK_SEL : 1 - DDRCLK pin provides the reference clock to the DDR PLL

*

*/

#include <../ls1046ardb/ls1046a.rcwi>

SYS_PLL_RAT=6

MEM_PLL_RAT=21

CGA_PLL1_RAT=16

CGA_PLL2_RAT=15

SRDS_PRTCL_S1=0

SRDS_PRTCL_S2=0

SRDS_PLL_PD_S1=3

SRDS_PLL_PD_S2=3

DDR_REFCLK_SEL=0

DDR_FDBK_MULT=2

PBI_src=4

IFC_MODE=37

HWA_CGA_M1_CLK_SEL=6

DRAM_LAT=1

UART_BASE=7

IRQ_OUT=1

IFC_GRP_A_EXT=1

IFC_GRP_E1_EXT=1

IFC_GRP_F_EXT=1

IFC_GRP_D_BASE=1

EC1=0

EC2=0

TVDD_VSEL=0

DVDD_VSEL=0

EVDD_VSEL=0

IIC2_EXT=0

SYSCLK_FREQ=600

HWA_CGA_M2_CLK_SEL=1

.pbi

// set CLK_SEL for QSPI CONFIG Register

write 0x57015c, 0x20100000

// set SCFG_SCRATCHRW1 ansd SCFG_SCRATCHRW2 for boot location ptr

write 0x570600, 0x00000000

write 0x570604, 0x40100000

.end

// Errta A-008850 for ddr controller for barrier transaction

#include <../ls1046ardb/cci_barrier_disable.rcw>

// Set USB PHY PLL for 100MHz

#include <../ls1046ardb/usb_phy_freq.rcw>

// Clear SerDes RxBoost on SD2 lane D

#include <../ls1046ardb/serdes_sata.rcw>

// Errata A-010477 and A-008851 for PCI Express Gen3 link training

#include <../ls1046ardb/pex_gen3_link.rcw>

.pbi

// QSPI END_CFG 64 bit LE

write 0x550000, 0x000f400c

.end

This results in the attached bl2_qspi.zip. Which I load up into the board and run the connection diagnostics tool without overwriting RCW it results in this:

Any tips to what I am doing wrong? Could you have a look at the RCW and spot any mistakes? I am specifically settings SRDS_PLL_PD_S1 and S2 to turn off Serdes for now.

Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please try the image bl2_qspi.pbl provided me again, I have verified it on LS1046AFRWY, I have passed all the diagnostics testing(including DDR read), then I sent it to you. I have attached it in this post again.

When you do flash programming, please remember to check erase action.

If you still have problem to use this image, please use flash programmer to dump the flash and save it to a file and send it to me.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for testing. I flashed it using erase and verify. All good.

Once i tried to run Centering the clock I get the same endianness error as before.

#################### Result for: wrlvl_searcher ###### Run 1 ######################################

Test result: [

============================================================

Updated: WRLVL_CNTL = 0x86750605, WRLVL_CNTL_2 = 0x00000000, WRLVL_CNTL_3 = 0x00000000, SDRAM_CLK_CNTL = 0x02800000

Traceback (most recent call last):

File "C:\Freescale\CW4NET_v2020.06\Common\QCVS\Optimization\resources\QorIQ\ARMv8/ddr/wrlvl_searcher.py", line 204, in write_leveling_start_searcher

debug = ddr_init.read_debug_regs(ddr_ctrl, session)

File "C:\Freescale\CW4NET_v2020.06\Common\QCVS\Optimization\resources\QorIQ\ARMv8\ddr\ddr_init.py", line 812, in read_debug_regs

swap = (ddr_ctrl['endianness'][default_space] == 'little_endian')

KeyError: 'endianness'

]

I have attached the dump from my QSPI.

fl_erase 0x0 0x9e00

Erased 39.50KB in 0.21s

fl_write 0x0 "C:\Users\Rinke\Downloads\bl2_qspi (1) (1)\bl2_qspi.pbl" --verify

Verify from 0x0 to 0x9dff succeeded

Wrote "C:/Users/Rinke/Downloads/bl2_qspi (1) (1)/bl2_qspi.pbl" in 0.77s

fl_dump 0x0 0x9dff -f "C:\Users\Rinke\Downloads\bl2_qspi (1) (1)\read_back_bl2.txt"

Dumped 39.50KB in 0.48s

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

No problem with your read back image.

After programming your read back image to my LS1046AFRWY demo board, I can perform the diagnose task and DDR Centering the clock validation successfully.

Please note you need to configure cfg_rcw_src[0:8] as 0_0100_010x to configure the target board boot from QSPI flash.

If your problem persists, please capture CCS console log to me to do more investigation.

After click "Start Validation" in QCVS DDR project, the CCS console will pop up in Windows task bar. Please open CCS and type "log v", then click "Start Validation" again, the low level CCS log will be printed out, please capture this log to me to do more investigation.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

There is problem with RCW loading. Please delete all PBI commands in your RCW configuration file to do verification.

The following RCW configurations are read from my target board, please try whether you could use these values to do RCW overriding with CodeWarrior.

RCWSR00: 0x0C150010

RCWSR01: 0x0E000000

RCWSR02: 0x00000000

RCWSR03: 0x00000000

RCWSR04: 0x00000000

RCWSR05: 0x00000002

RCWSR06: 0x40000000

RCWSR07: 0xC1000000

RCWSR08: 0x00000000

RCWSR09: 0x00000000

RCWSR10: 0x00000000

RCWSR11: 0x00000800

RCWSR12: 0x00000000

RCWSR13: 0x00000000

RCWSR14: 0x00000096

RCWSR15: 0x00000001

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

When I use your exact RCW values I am getting this:

I emptied the QSPI memory before to make sure nothing is interfering.

Your RCW itself does not work for me. Once I change RCW5 to 0x00f00002. So powering down the Serdes and uncommenting 6 (For selecting QSPI boot) it will work for me.

TA.rcw.set_data({1: 0x0C150010})

TA.rcw.set_data({2: 0x0e000000})

TA.rcw.set_data({3: 0x00000000})

TA.rcw.set_data({4: 0x00000000})

TA.rcw.set_data({5: 0x00000000})

TA.rcw.set_data({6: 0x00f00002})

#TA.rcw.set_data({7: 0x40000000})

TA.rcw.set_data({8: 0xc1000000})

TA.rcw.set_data({9: 0x00000000})

TA.rcw.set_data({10: 0x00000000})

TA.rcw.set_data({11: 0x00000000})

# Configure UART

TA.rcw.set_data({12: 0x00000800})

# Configure QSPI

TA.rcw.set_data({13: 0x00000000})

TA.rcw.set_data({14: 0x00000000})

TA.rcw.set_data({15: 0x00000096})

TA.rcw.set_data({16: 0x00000001})

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I generated file bl2_qspi.pbl with your RCW configuration, please extract the attached file and program it at offset 0 of your QSPI flash, and configure cfg_rcw_src[0:8] as 0_0100_0100, then do verification.

If your problem persists, please create a QCVS PBL project in CodeWarrior to check whether it is possible to read RCW from the target board.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hey

So we got BL2 working. I needed to uncomment the first PBI instruction that was generic in the freeway config. We are using a different DRAM chip compared to the Freeway. Once we made some changes in BL2 we get the message below. Im assuming ddr controller initialized properly? I tried to run ddrv tool now but it doesnt do anything.

Err. capture registers:

0xE20, 0x00000000 0xE24, 0x00000000 0xE28, 0x00000000 0xE40, 0x00000080

0xE44, 0x00000000 0xE48, 0x00000000 0xE4C, 0x00000000 0xE50, 0x00000000

0xE54, 0x00000000 0xE58, 0x00010000

Dump:

0xF00, 0x00000000 0xF04, 0x00003002 0xF08, 0x00000010 0xF0C, 0x14000C20

0xF10, 0x00000000 0xF14, 0x00000000 0xF18, 0x00000000 0xF1C, 0x00000000

0xF20, 0x00000000 0xF24, 0x10101010 0xF28, 0x10101010 0xF2C, 0x10101010

0xF30, 0x10101010 0xF34, 0x10103000 0xF38, 0x00000000 0xF3C, 0x00000000

0xF40, 0x00000000 0xF44, 0x00000000 0xF48, 0x00000001 0xF4C, 0x94000000

0xF50, 0x3C003B00 0xF54, 0x3D003D00 0xF58, 0x30003000 0xF5C, 0x31003200

0xF60, 0x2F000000 0xF64, 0x00009000 0xF68, 0x00000021 0xF6C, 0x00000000

0xF70, 0x0080006A 0xF74, 0x00000000 0xF78, 0x00000000 0xF7C, 0x00000000

0xF80, 0x00000000 0xF84, 0x00000000 0xF88, 0x00000000 0xF8C, 0x00000000

0xF90, 0x00000000 0xF94, 0x80000000 0xF98, 0x00000000 0xF9C, 0x02020202

0xFA0, 0x02020202 0xFA4, 0x02020202 0xFA8, 0x02020202 0xFAC, 0x02020000

0xFB0, 0x00000003 0xFB4, 0x1F1F1F1F 0xFB8, 0x1F1F1F1F 0xFBC, 0x1F1F1F1F

0xFC0, 0x1F1F1F1F 0xFC4, 0x1F1F1F1F 0xFC8, 0x1F1F1F1F 0xFCC, 0x1F1F1F1F

0xFD0, 0x1F1F1F1F 0xFD4, 0x1F1F1F1F 0xFD8, 0x1F1F1F1F 0xFDC, 0x1F1F1F1F

0xFE0, 0x1F1F1F1F 0xFE4, 0x1F1F1F1F 0xFE8, 0x1F1F1F1F 0xFEC, 0x1F1F1F1F

0xFF0, 0x1F1F1F1F 0xFF4, 0x1F1F1F1F 0xFF8, 0x1F1F1F1F 0xFFC, 0x1F004740

Data:

0x00000005 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000

]When I check ccs logv it just gets stuck on the next line. See CCS log for full log

read_memory(coreh.{serverh=0,cc_index=0,chain_pos=17},

addr.{addr_hi=0x00000000,addr_lo=0x01080114,size=4,space=4607},count=4,*data)

data: 00401052

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- When creating a QCVS DDR project, in DDR configuration panel, please select configuration mode as "From memory file" and "Discrete DRAM" and specify the input file as the attached CodeWarrior Register Text file.

- Please double click "DDR_mc1:DDR" to open Properties panel, please modify parameters in Properties panel according to your DDR datasheet and the schematics of your target board.

Then save the configurations to do DDR validation.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Does not make a difference. Can you tell me exactly in what state the board should be in to run the DDRv tool? When running just BL2 the cpu gets stuck trying to load BL3. Logically. But is that oke for the DDRv tool? D_Init is cleared by our BL2 so the ddr controller should be initialized for the ddrv tool to take over? When running BIST in BL2 it fails on training. Any tips?

ERROR: Found training error(s): 0x3002

ERROR: Writing DDR register(s) failed 0

ERROR: Programing DDRC error

INFO: DRAM size 0xfffffffffffffffb

ERROR: DDR init failed.