- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- QorIQ Processing Platforms

- :

- Layerscape

- :

- CW SPD Read failure

CW SPD Read failure

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

CW SPD Read failure

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

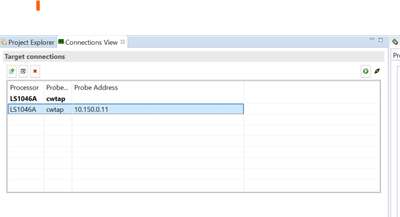

I have a custom board based on LS1046A, with a DDR4 SODIMM and I am validating a new DDR4 module using the DDR validation tool. However, I can't read the SPD from the CW. The SPD_EEPROM_ADDRESS is 0x50, and SPD_BUS_NUM is 1.

I have checked C:\Freescale\CW4NET_v2020.06\Common\QCVS\Optimization\resources\QorIQ\ARMv8\templates\ddr\system_config_params_read_spd.json, The 0x50 is listed here but I cannot find a place to set the bus number.

"in" : {

"spd_eeprom_addrs" : "0x50 0x51 0x52 0x53 0x54 0x55 0x56 0x57",

"i2c_mux_addrs" : "<<{I2C_MUX}>>",

"i2c_mux_ch_default" : "0x8"

},

"Read SPD" from DDR configuration tool does not work. Probe connection is fine.

I have tried to manually setup the project by using a known working reg file (created for a different DDR CBD26D4S9S1KC-4 ) and then reading the SPD using FSL-DDR, and modified non matching settings, but that project has Validation failures, so I am trying to directly read the SPD from the CW.

FSL DDR>print dimm

SPD info: Controller=0 DIMM=0

0 : 23 info_size_crc bytes written into serial memory, CRC coverage

1 : 11 spd_rev SPD Revision

2 : 0c mem_type Key Byte / DRAM Device Type

3 : 03 module_type Key Byte / Module Type

4 : 84 density_banks SDRAM Density and Banks

5 : 19 addressing SDRAM Addressing

6 : 00 package_type Package type

7 : 08 opt_feature Optional features

8 : 00 thermal_ref Thermal and Refresh options

9 : 60 oth_opt_features Other SDRAM optional features

10 : 00 res_10 Reserved

11 : 03 module_vdd Module Nominal Voltage, VDD

12 : 01 organization Module Organization

13 : 03 bus_width Module Memory Bus Width

14 : 00 therm_sensor Module Thermal Sensor

15 : 00 ext_type Extended module type

16 : 00 res_16 Reserved

17 : 00 timebases MTb and FTB

18 : 06 tck_min tCKAVGmin

19 : 0d tck_max TCKAVGmax

20 : f8 caslat_b1 CAS latencies, 1st byte

21 : 3f caslat_b2 CAS latencies, 2nd byte

22 : 00 caslat_b3 CAS latencies, 3rd byte

23 : 00 caslat_b4 CAS latencies, 4th byte

24 : 6e taa_min Min CAS Latency Time

25 : 6e trcd_min Min RAS# to CAS# Delay Time

26 : 6e trp_min Min Row Precharge Delay Time

27 : 11 tras_trc_ext Upper Nibbles for tRAS and tRC

28 : 00 tras_min_lsb tRASmin, lsb

29 : 6e trc_min_lsb tRCmin, lsb

30 : 20 trfc1_min_lsb Min Refresh Recovery Delay Time, LSB

31 : 08 trfc1_min_msb Min Refresh Recovery Delay Time, MSB

32 : 00 trfc2_min_lsb Min Refresh Recovery Delay Time, LSB

33 : 05 trfc2_min_msb Min Refresh Recovery Delay Time, MSB

34 : 70 trfc4_min_lsb Min Refresh Recovery Delay Time, LSB

35 : 03 trfc4_min_msb Min Refresh Recovery Delay Time, MSB

36 : 00 tfaw_msb Upper Nibble for tFAW

37 : a8 tfaw_min tFAW, lsb

38 : 18 trrds_min tRRD_Smin, MTB

39 : 28 trrdl_min tRRD_Lmin, MTB

40 : 28 tccdl_min tCCS_Lmin, MTB

41 - 59: 00 78 00 14 3c 00 00 00 00 00 00 00 00 00 00 00 00 00 00

60 - 77: 0c 2b 2d 04 16 35 23 0d 00 00 2c 0b 03 24 35 0c 03 2d mapping[] Connector to SDRAM bit map

117 : 00 fine_tccdl_min Fine offset for tCCD_Lmin

118 : 9c fine_trrdl_min Fine offset for tRRD_Lmin

119 : 00 fine_trrds_min Fine offset for tRRD_Smin

120 : 00 fine_trc_min Fine offset for tRCmin

121 : 00 fine_trp_min Fine offset for tRPmin

122 : 00 fine_trcd_min Fine offset for tRCDmin

123 : 00 fine_taa_min Fine offset for tAAmin

124 : e7 fine_tck_max Fine offset for tCKAVGmax

125 : 00 fine_tck_min Fine offset for tCKAVGmin

126-127: 64 20 SPD CRC

128 : 0f mod_height (Unbuffered) Module Nominal Height

129 : 11 mod_thickness (Unbuffered) Module Maximum Thickness

130 : 00 ref_raw_card (Unbuffered) Reference Raw Card Used

131 : 00 addr_mapping (Unbuffered) Address mapping from Edge Connector to DRAM

254-255: 45 ad Module CRC

320 : 07 Module MfgID Code LSB - JEP-106

321 : f7 Module MfgID Code MSB - JEP-106

322 : 00 Mfg Location

323-324: 24 39 Mfg Date

325-328: 09 23 00 02 Module Serial Number

329-348: 43 4d 42 36 2d 35 46 41 31 30 42 41 52 30 31 55 55 30 20 20 Mfg's Module Part Number

349 : 00 Module Revision code

350 : 80 DRAM MfgID Code LSB - JEP-106

351 : ce DRAM MfgID Code MSB - JEP-106

352 : 00 DRAM stepping

353-381: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 Mfg's Specific Data

DIMM parameters: Controller=0 DIMM=0

DIMM organization parameters:

module part name = CMB6-5FA10BAR01UU0

rank_density = 4294967296 bytes (4096 megabytes)

capacity = 4294967296 bytes (4096 megabytes)

burst_lengths_bitmask = 0C

base_addresss = 0 (00000000 00000000)

n_ranks = 1

data_width = 64

primary_sdram_width = 64

ec_sdram_width = 0

package_3ds = 0

registered_dimm = 0

mirrored_dimm = 0

device_width = 8

n_row_addr = 15

n_col_addr = 10

edc_config = 0

bank_addr_bits = 0

bank_group_bits = 2

die_density = 0x00000004

tckmin_x_ps = 750

tckmin_x_minus_1_ps = 0

tckmin_x_minus_2_ps = 0

tckmax_ps = 1600

caslat_x = 2096128

caslat_x = 0x001FFC00

taa_ps = 13750

caslat_x_minus_1 = 0

caslat_x_minus_2 = 0

caslat_lowest_derated = 0

trcd_ps = 13750

trp_ps = 13750

tras_ps = 32000

tfaw_ps = 21000

trfc1_ps = 260000

trfc2_ps = 160000

trfc4_ps = 110000

trrds_ps = 3000

trrdl_ps = 4900

tccdl_ps = 5000

trfc_slr_ps = 0

trc_ps = 45750

refresh_rate_ps = 7800000

dq_mapping[0] = 0x0000000C

dq_mapping[1] = 0x0000002B

dq_mapping[2] = 0x0000002D

dq_mapping[3] = 0x00000004

dq_mapping[4] = 0x00000016

dq_mapping[5] = 0x00000035

dq_mapping[6] = 0x00000023

dq_mapping[7] = 0x0000000D

dq_mapping[8] = 0x00000000

dq_mapping[9] = 0x00000000

dq_mapping[10] = 0x0000002C

dq_mapping[11] = 0x0000000B

dq_mapping[12] = 0x00000003

dq_mapping[13] = 0x00000024

dq_mapping[14] = 0x00000035

dq_mapping[15] = 0x0000000C

dq_mapping[16] = 0x00000003

dq_mapping[17] = 0x0000002D

dq_mapping_ors = 1

"lowest common" DIMM parameters: Controller=0

tckmin_x_ps = 750 (1333 MHz)

tckmax_ps = 1600 (625 MHz)

all_dimms_burst_lengths_bitmask = 0C

taamin_ps = 13750

trcd_ps = 13750

trp_ps = 13750

tras_ps = 32000

trfc1_ps = 260000

trfc2_ps = 160000

trfc4_ps = 110000

trrds_ps = 3000

trrdl_ps = 4900

tccdl_ps = 5000

trfc_slr_ps = 0

twr_ps = 15000

trc_ps = 45750

refresh_rate_ps = 7800000

extended_op_srt = 0

lowest_common_spd_caslat = 11

highest_common_derated_caslat = 0

additive_latency = 0

ndimms_present = 1

all_dimms_registered = 0

all_dimms_unbuffered = 1

all_dimms_ecc_capable = 0

total_mem = 4294967296 (4096 megabytes)

base_address = 0 (0 megabytes)

User Config Options: Controller=0

cs0_odt_rd_cfg = 0

cs0_odt_wr_cfg = 4

cs1_odt_rd_cfg = 0

cs1_odt_wr_cfg = 0

cs2_odt_rd_cfg = 0

cs2_odt_wr_cfg = 0

cs3_odt_rd_cfg = 0

cs3_odt_wr_cfg = 0

cs0_odt_rtt_norm = 3

cs0_odt_rtt_wr = 0

cs1_odt_rtt_norm = 0

cs1_odt_rtt_wr = 0

cs2_odt_rtt_norm = 0

cs2_odt_rtt_wr = 0

cs3_odt_rtt_norm = 0

cs3_odt_rtt_wr = 0

memctl_interleaving = 0

memctl_interleaving_mode = 0

ba_intlv_ctl = 0x00000000

ecc_mode = 1

ecc_init_using_memctl = 1

dqs_config = 0

self_refresh_in_sleep = 1

dynamic_power = 0

data_bus_width = 0

burst_length = 6

cas_latency_override = 0

cas_latency_override_value = 3

use_derated_caslat = 0

additive_latency_override = 0

additive_latency_override_value = 3

clk_adjust = 8

cpo_override = 0

write_data_delay = 0

half_strength_driver_enable = 0

twot_en = 0

threet_en = 0

registered_dimm_en = 0

mirrored_dimm = 0

ap_en = 0

x4_en = 0

package_3ds = 0

bstopre = 0

wrlvl_override = 1

wrlvl_sample = 15

wrlvl_start = 17

cswl_override = 0x00000000

rcw_override = 0

rcw_1 = 0x00000000

rcw_2 = 0x00000000

rcw_3 = 0x00000000

ddr_cdr1 = 0x80040000

ddr_cdr2 = 0x000000C1

tfaw_window_four_activates_ps = 21000

trwt_override = 0

trwt = 0

rtt_override = 0

rtt_override_value = 0

rtt_wr_override_value = 0

Address Assignment: Controller=0 DIMM=0

Don't have this functionality yet

Computed Register Values: Controller=0

cs0_bnds = 0x000000FF

cs0_config = 0x80040322

cs0_config_2 = 0x00000000

cs1_bnds = 0x00000000

cs1_config = 0x00000000

cs1_config_2 = 0x00000000

cs2_bnds = 0x00000000

cs2_config = 0x00000000

cs2_config_2 = 0x00000000

cs3_bnds = 0x00000000

cs3_config = 0x00000000

cs3_config_2 = 0x00000000

timing_cfg_3 = 0x010C1000

timing_cfg_0 = 0x91550018

timing_cfg_1 = 0xBAB48E44

timing_cfg_2 = 0x00490111

ddr_sdram_cfg = 0xC5000000

ddr_sdram_cfg_2 = 0x00401150

ddr_sdram_cfg_3 = 0x00000000

ddr_sdram_mode = 0x03010211

ddr_sdram_mode_2 = 0x00000000

ddr_sdram_mode_3 = 0x00010211

ddr_sdram_mode_4 = 0x00000000

ddr_sdram_mode_5 = 0x00010211

ddr_sdram_mode_6 = 0x00000000

ddr_sdram_mode_7 = 0x00010211

ddr_sdram_mode_8 = 0x00000000

ddr_sdram_mode_9 = 0x00000500

ddr_sdram_mode_10 = 0x00400000

ddr_sdram_mode_11 = 0x00000400

ddr_sdram_mode_12 = 0x00400000

ddr_sdram_mode_13 = 0x00000400

ddr_sdram_mode_14 = 0x00400000

ddr_sdram_mode_15 = 0x00000400

ddr_sdram_mode_16 = 0x00400000

ddr_sdram_interval = 0x18600000

ddr_data_init = 0xDEADBEEF

ddr_sdram_clk_cntl = 0x02000000

ddr_init_addr = 0x00000000

ddr_init_ext_addr = 0x00000000

timing_cfg_4 = 0x00220002

timing_cfg_5 = 0x03401400

timing_cfg_6 = 0x00000000

timing_cfg_7 = 0x13300000

timing_cfg_8 = 0x01224800

timing_cfg_9 = 0x00000000

ddr_zq_cntl = 0x8A090705

ddr_wrlvl_cntl = 0x8675F611

ddr_wrlvl_cntl_2 = 0x06000000

ddr_wrlvl_cntl_3 = 0x00000000

ddr_sr_cntr = 0x00000000

ddr_sdram_rcw_1 = 0x00000000

ddr_sdram_rcw_2 = 0x00000000

ddr_sdram_rcw_3 = 0x00000000

ddr_cdr1 = 0x80040000

ddr_cdr2 = 0x000000C1

dq_map_0 = 0x32BB4458

dq_map_1 = 0xD6336C2C

dq_map_2 = 0x0E4D4C0C

dq_map_3 = 0xB4000001

err_disable = 0x00000000

err_int_en = 0x00000000

ddr_eor = 0x00000000

debug_01 = 0x00000000

debug_02 = 0x00000000

debug_03 = 0x00000000

debug_04 = 0x00000000

debug_05 = 0x00000000

debug_06 = 0x00000000

debug_07 = 0x00000000

debug_08 = 0x00000000

debug_09 = 0x00000000

debug_10 = 0x00000000

debug_11 = 0x00000000

debug_12 = 0x00000000

debug_13 = 0x00000000

debug_14 = 0x00000000

debug_15 = 0x00000000

debug_16 = 0x00000000

debug_17 = 0x00000000

debug_18 = 0x00000000

debug_19 = 0x00000000

debug_20 = 0x00000000

debug_21 = 0x00000000

debug_22 = 0x00000000

debug_23 = 0x00000000

debug_24 = 0x00000000

debug_25 = 0x00000000

debug_26 = 0x00000000

debug_27 = 0x00000000

debug_28 = 0x00000000

debug_29 = 0x00700061

debug_30 = 0x00000000

debug_31 = 0x00000000

debug_32 = 0x00000000

debug_33 = 0x00000000

debug_34 = 0x00000000

debug_35 = 0x00000000

debug_36 = 0x00000000

debug_37 = 0x00000000

debug_38 = 0x00000000

debug_39 = 0x00000000

debug_40 = 0x00000000

debug_41 = 0x00000000

debug_42 = 0x00000000

debug_43 = 0x00000000

debug_44 = 0x00000000

debug_45 = 0x00000000

debug_46 = 0x00000000

debug_47 = 0x00000000

debug_48 = 0x00000000

debug_49 = 0x00000000

debug_50 = 0x00000000

debug_51 = 0x00000000

debug_52 = 0x00000000

debug_53 = 0x00000000

debug_54 = 0x00000000

debug_55 = 0x00000000

debug_56 = 0x00000000

debug_57 = 0x00000000

debug_58 = 0x00000000

debug_59 = 0x00000000

debug_60 = 0x00000000

debug_61 = 0x00000000

debug_62 = 0x00000000

debug_63 = 0x00000000

debug_64 = 0x00000000

FSL DDR>

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

For reading from SPD, would you please click "X" and send the whole error log to me?