- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- LPCマイクロコントローラ

- :

- Re: unable to configure UART1 on LPC1124 microcontroller

unable to configure UART1 on LPC1124 microcontroller

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

unable to configure UART1 on LPC1124 microcontroller

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

This piece of code works perfect to setup UART0. After this the UART0 works just fine.

/* Setup UART for 9600 */

Chip_UART_Init(LPC_UART0);

Chip_UART_SetBaud(LPC_UART0, 9600);

Chip_UART_ConfigData(LPC_UART0, (UART_LCR_WLEN8 | UART_LCR_SBS_1BIT));

Chip_UART_SetupFIFOS(LPC_UART0, (UART_FCR_FIFO_EN | UART_FCR_TRG_LEV2));

Chip_UART_TXEnable(LPC_UART0);

The piece of code underneath doesn't effect the UART1 registers at all ? What could be the reason of this ? I just changed the UART0 to UART1 and if i debug i can see the addresses are right...

Chip_UART_Init(LPC_UART1);

Chip_UART_SetBaud(LPC_UART1, 9600);

Chip_UART_ConfigData(LPC_UART1, (UART_LCR_WLEN8 | UART_LCR_SBS_1BIT));

Chip_UART_SetupFIFOS(LPC_UART1, (UART_FCR_FIFO_EN | UART_FCR_TRG_LEV2));

Chip_UART_TXEnable(LPC_UART1);

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi pascal carreweyn,

Thank you for your interest in NXP Semiconductor products and for the opportunity to serve you.

Please assure the UART pin configuration is correct, in further, check interrupt configuration.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

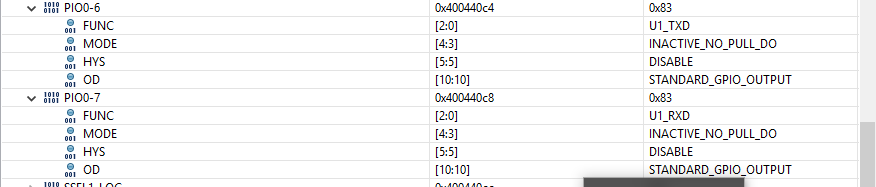

if i debug the next code

Chip_IOCON_PinMuxSet(LPC_IOCON, IOCON_PIO0_7, (IOCON_FUNC3 | IOCON_MODE_INACT)); /* RXD1 */

Chip_IOCON_PinMuxSet(LPC_IOCON, IOCON_PIO0_6, (IOCON_FUNC3 | IOCON_MODE_INACT)); /* TXD1 */

Nothing happens in the IOCON register when i do the code above....

if i do this code for the uart0? this changes the register IOCON

Chip_IOCON_PinMuxSet(LPC_IOCON, IOCON_PIO1_6, (IOCON_FUNC1 | IOCON_MODE_INACT | IOCON_DIGMODE_EN)); /* RXD0 */

Chip_IOCON_PinMuxSet(LPC_IOCON, IOCON_PIO1_7, (IOCON_FUNC1 | IOCON_MODE_INACT | IOCON_DIGMODE_EN)); /* TXD0 */

i have no idea why this is the case ?

Please explain me what's happening ?

If this is unclear, please provide me an example where PIO0_7 and PIO0_6 is used as UART1

Greetings,

Pascal

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi pascal carreweyn,

Thanks for your reply.

It seems a bit weird, so please confirm that the correct address areas are written.

I was wondering if you can share a compile-able demo which can replicate this phenomenon, then I can do some testing on my site.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi pascal carreweyn,

Thanks for your reply.

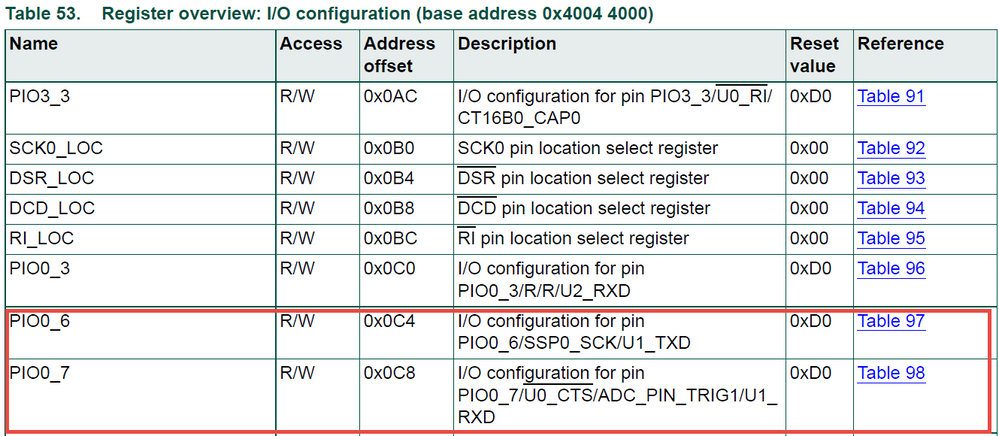

After having a brief review of the code, I find that the address definition of PIO0_6 and PIO0_7 is not consistent with Table 53 illustrates in the UM10839.

So please use the modified code to give a try.

...

IOCON_PIO0_6 = (0x0C4 >> 2),

IOCON_PIO0_7 = (0x0C8 >> 2),

...Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Jeremy,

Now the pio0 6 and pio 07 are configured as uart, the problem was the wrong address.

But now my previous problem stays !!!

The piece of code underneath doesn't effect the UART1 registers at all ? What could be the reason of this ? I just changed the UART0 to UART1 and if i debug i can see the addresses are right...

Chip_UART_Init(LPC_UART1);

Chip_UART_SetBaud(LPC_UART1, 9600);

Chip_UART_ConfigData(LPC_UART1, (UART_LCR_WLEN8 | UART_LCR_SBS_1BIT));

Chip_UART_SetupFIFOS(LPC_UART1, (UART_FCR_FIFO_EN | UART_FCR_TRG_LEV2));

Chip_UART_TXEnable(LPC_UART1);

I also thought there would be a wrong address but it seems to be something else ?

in the chip.h we have

#define LPC_UART0_BASE 0x40008000

#define LPC_UART1_BASE 0x40020000

#define LPC_UART2_BASE 0x40024000

...

#define LPC_UART0 ((LPC_UART_T *) LPC_UART0_BASE)

#define LPC_UART1 ((LPC_UART_T *) LPC_UART1_BASE)

#define LPC_UART2 ((LPC_UART_T *) LPC_UART2_BASE)

in the uart_112x.h we have

/**

* @brief UART register block structure

*/

typedef struct { /*!< UARTn Structure */

union {

__IO uint32_t DLL; /*!< Divisor Latch LSB. Least significant byte of the baud rate divisor value. The full divisor is used to generate a baud rate from the fractional rate divider (DLAB = 1). */

__O uint32_t THR; /*!< Transmit Holding Register. The next character to be transmitted is written here (DLAB = 0). */

__I uint32_t RBR; /*!< Receiver Buffer Register. Contains the next received character to be read (DLAB = 0). */

};

union {

__IO uint32_t IER; /*!< Interrupt Enable Register. Contains individual interrupt enable bits for the 7 potential UART interrupts (DLAB = 0). */

__IO uint32_t DLM; /*!< Divisor Latch MSB. Most significant byte of the baud rate divisor value. The full divisor is used to generate a baud rate from the fractional rate divider (DLAB = 1). */

};

union {

__O uint32_t FCR; /*!< FIFO Control Register. Controls UART FIFO usage and modes. */

__I uint32_t IIR; /*!< Interrupt ID Register. Identifies which interrupt(s) are pending. */

};

__IO uint32_t LCR; /*!< Line Control Register. Contains controls for frame formatting and break generation. */

__IO uint32_t MCR; /*!< Modem Control Register. Only present on UART ports with full modem support. */

__I uint32_t LSR; /*!< Line Status Register. Contains flags for transmit and receive status, including line errors. */

__I uint32_t MSR; /*!< Modem Status Register. Only present on UART ports with full modem support. */

__IO uint32_t SCR; /*!< Scratch Pad Register. Eight-bit temporary storage for software. */

__IO uint32_t ACR; /*!< Auto-baud Control Register. Contains controls for the auto-baud feature. */

__I uint32_t RESERVED0;

__IO uint32_t FDR; /*!< Fractional Divider Register. Generates a clock input for the baud rate divider. */

__I uint32_t RESERVED1;

__IO uint32_t TER; /*!< Transmit Enable Register. Turns off UART transmitter for use with software flow control. */

__I uint32_t RESERVED2[6];

__IO uint32_t RS485CTRL; /*!< RS-485/EIA-485 Control. Contains controls to configure various aspects of RS-485/EIA-485 modes. */

__IO uint32_t RS485ADRMATCH; /*!< RS-485/EIA-485 address match. Contains the address match value for RS-485/EIA-485 mode. */

__IO uint32_t RS485DLY; /*!< RS-485/EIA-485 direction control delay. */

} LPC_UART_T;

/**

Any idea what's going on ?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi pascal carreweyn,

Thanks for your reply.

After reviewing the demo code carefully, I find that it's unable to enable the clock to the UART1 by calling the Chip_UART_Init(LPC_UART1);.

In the following void Chip_UART_Init(LPC_UART_T *pUART) function,

/* Initializes the pUART peripheral */

void Chip_UART_Init(LPC_UART_T *pUART)

{

Chip_Clock_EnablePeriphClock(SYSCON_CLOCK_UART0); //It's the cause of the issue

Chip_Clock_SetUARTClockDiv(1);

/* Enable FIFOs by default, reset them */

Chip_UART_SetupFIFOS(pUART, (UART_FCR_FIFO_EN | UART_FCR_RX_RS | UART_FCR_TX_RS));

/* Default 8N1, with DLAB disabled */

Chip_UART_ConfigData(pUART, (UART_LCR_WLEN8 | UART_LCR_SBS_1BIT | UART_LCR_PARITY_DIS));

/* Disable fractional divider */

pUART->FDR = 0x10;

}it's impossible to enable other UART's clock except for the UART0.

It's the cause of the issue, please to do some modifications about the Chip_Clock_EnablePeriphClock(SYSCON_CLOCK_UART0); to enable the clock to the UART1.

Hope it helps.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Jeremy,

The addresses are defined in a header file : gpio_112x.h

which i got from an lpc open project

here is a part of the definition

typedef enum CHIP_IOCON_PIO {

IOCON_PIO0_0 = (0x00C >> 2),

IOCON_PIO0_1 = (0x010 >> 2),

IOCON_PIO0_2 = (0x01C >> 2),

IOCON_PIO0_3 = (0x02C >> 2),

IOCON_PIO0_4 = (0x030 >> 2),

IOCON_PIO0_5 = (0x034 >> 2),

IOCON_PIO0_6 = (0x04C >> 2),

IOCON_PIO0_7 = (0x050 >> 2),

...

this part form chip.h

#define LPC_IOCON_BASE 0x40044000

#define LPC_IOCON ((LPC_IOCON_T *) LPC_IOCON_BASE)

I also sent the test project files in the attachment on a reply of your email. (i use Version: MCUXpresso IDE v10.3.0 [Build 2200] [2018-12-03])

If you want we can also do a teamviewer session so i can show you what's the problem.

Pascal