- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- Re: forced hard fault generated by escalation of a fault with configurable priority that cannot be handled

forced hard fault generated by escalation of a fault with configurable priority that cannot be handled

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

forced hard fault generated by escalation of a fault with configurable priority that cannot be handled

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

my project runinto hardfault, the info below:

Stack:

Thread #1 57005 (Suspended : Signal : SIGTRAP:Trace/breakpoint trap)

HardFault_Handler() at semihost_hardfault.c:72 0x1da54

<signal handler called>() at 0xfffffff1

xTaskIncrementTick() at tasks.c:2,705 0x1a4c4

SysTick_Handler() at port.c:447 0x19510

<signal handler called>() at 0xffffffed

prvPortStartFirstTask() at port.c:217 0x19304

xPortStartScheduler() at port.c:329 0x19412

Faults info:

Active faults @\amazon-freertos\FreeRTOS\tasks.c line 2707

Bus Fault (BFSR)

BFARVALID (7) BusFault Address Register (BFAR) valid flag

PRECISERR (1) Precise data bus errorHard Fault (HFSR)

FORCED (30) Indicates a forced hard fault, generated by escalation of a fault with configurable priority that cannot be handled, either because of priority or because it is disabled

Fault Status RegistersIPSR 0x00000003 Exception Status Register (Hard Fault)

CFSR 0x00008200 Configurable fault Status Register

MMSR 0x00000000 Memory Manage fault Status Register

BFSR 0x00000082 Bus fault Status Register

UFSR 0x00000000 User fault Status Register

HFSR 0x40000000 Hard fault Status Register

DFSR 0x00000001 Debug fault Status Register

MMAR 0x3805C938 Memory Manage fault Address Register

BFAR 0x3805C938 Bus fault Address Register

AFSR 0x00000000 Auxiliary fault Status Register

Stacked Registers (SP LR/EXC_RETURN=0xfffffff1)R0 0x00000003

R1 0x2001CCAC

R2 0x0E003307

R3 0x3805C938

R12 0x000000AA

LR 0x00018E25 SysTick_Handler() @ \amazon-freertos\FreeRTOS\portable\port.c line 451

PC 0x00019DD8 xTaskIncrementTick()

PSR 0x2100000FSP 0x20027F90

my project info:

MCU:LPC54606

OS:FreeRTOS

Middleware:Lwip with SDK

SDK:2.4.1

Interrupt used: Enet by LWIP with Priority 6

PINT0,PINT1 with no Priority settings, default priority?

peripherals used: flexcomm0(SPI poll mode), flexcomm3(SPI poll mode),

5 GPIOs

the FreeRTOSConfig.h settings as below:

#define configUSE_PREEMPTION 1

#define configUSE_TICKLESS_IDLE 0

#define configCPU_CLOCK_HZ (SystemCoreClock)

#define configTICK_RATE_HZ ((TickType_t)100)

#define configMAX_PRIORITIES 5

#define configMINIMAL_STACK_SIZE ((unsigned short)100)

#define configMAX_TASK_NAME_LEN 10

#define configUSE_16_BIT_TICKS 0

#define configIDLE_SHOULD_YIELD 1

#define configUSE_TASK_NOTIFICATIONS 1

#define configUSE_MUTEXES 1

#define configUSE_RECURSIVE_MUTEXES 1//0 liang 5.23

#define configUSE_COUNTING_SEMAPHORES 1

#define configUSE_ALTERNATIVE_API 0 /* Deprecated! */

#define configQUEUE_REGISTRY_SIZE 8

#define configUSE_QUEUE_SETS 0

#define configUSE_TIME_SLICING 1//

#define configUSE_NEWLIB_REENTRANT 0

#define configENABLE_BACKWARD_COMPATIBILITY 1

#define configNUM_THREAD_LOCAL_STORAGE_POINTERS 5

#define configUSE_APPLICATION_TASK_TAG 0

... ...#ifdef __NVIC_PRIO_BITS

/* __BVIC_PRIO_BITS will be specified when CMSIS is being used. */

#define configPRIO_BITS __NVIC_PRIO_BITS

#else

#define configPRIO_BITS 3 /* 15 priority levels */

#endif

/* The lowest interrupt priority that can be used in a call to a "set priority"

function. */

#define configLIBRARY_LOWEST_INTERRUPT_PRIORITY 7//((1U << (configPRIO_BITS)) - 1)//7

/* The highest interrupt priority that can be used by any interrupt service

routine that makes calls to interrupt safe FreeRTOS API functions. DO NOT CALL

INTERRUPT SAFE FREERTOS API FUNCTIONS FROM ANY INTERRUPT THAT HAS A HIGHER

PRIORITY THAN THIS! (higher priorities are lower numeric values. */

#define configLIBRARY_MAX_SYSCALL_INTERRUPT_PRIORITY 2//liang 5.23

/* Interrupt priorities used by the kernel port layer itself. These are generic

to all Cortex-M ports, and do not rely on any particular library functions. */

#define configKERNEL_INTERRUPT_PRIORITY (configLIBRARY_LOWEST_INTERRUPT_PRIORITY << (8 - configPRIO_BITS))

/* !!!! configMAX_SYSCALL_INTERRUPT_PRIORITY must not be set to zero !!!!

See http://www.FreeRTOS.org/RTOS-Cortex-M3-M4.html. */

#define configMAX_SYSCALL_INTERRUPT_PRIORITY (configLIBRARY_MAX_SYSCALL_INTERRUPT_PRIORITY << (8 - configPRIO_BITS))

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi liang chen,

I had the same problem, in my case the issue was created have write in two different place this function " vTaskStartScheduler();"

Best Regards

Marco

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have seen this post:FreeRTOS bug in xQueueGenericSendFromISR ?

I thinks they say wrong in the post ,

"Content originally posted in LPCWare by alramlechner on Fri Aug 07 13:28:29 MST 2015

just found it. IRQ priority, which uses FreeRTOS API, must have lower priority than SysTick ... "

actually all other IRQ priority should have higher priority than Systick(configKERNEL_INTERRUPT_PRIORITY), and lower than configLIBRARY_MAX_SYSCALL_INTERRUPT_PRIORITY (http://www.freertos.org/a00110.html#kernel_priority).

my project follow this rule , but hardfault still. i don't know why.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

could someone help on this.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, LiangChen,

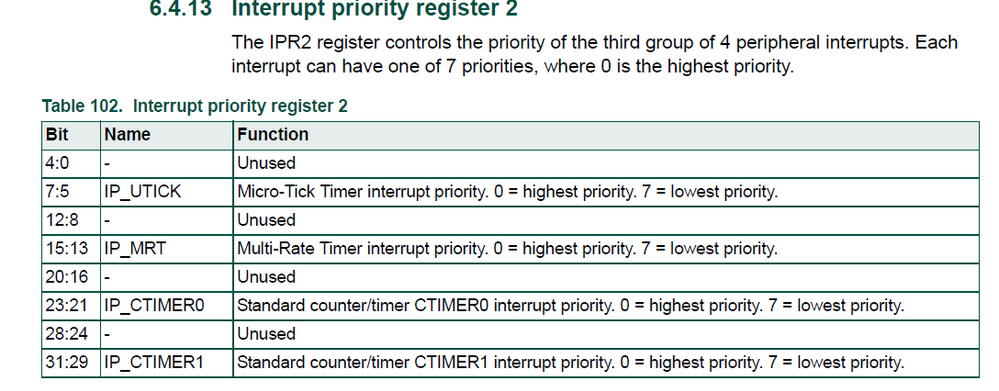

As you know that the Cortex-M4 use the follow IPR register format for each external interrupt source:

For example, the interrupt priority of IP_CTIMER0 for LPC546xx are located at bit21~23, it's priority is from 0 to 7(from 3b'000 to 3b'111), the 3b'000 is of highest priority, the 3b'111 is of lowest priority. The configMAX_PRIORITIES is set up as 5 using the line in FreeRtos system:

#define configMAX_PRIORITIES 5

So for your own peripheral interrupt source, you have to set priority of your own peripheral interrupt source lower than 5 level. In other words, set the IPR register value greater than 5. For example, you want to use IP_TIMER0 module interrupt, and post an event, so you have to set up the IP_CTIMER0 bits(bit21~23) for example 6, 3b'110, it is okay.

Hope it can help you

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Rong

thanks for helping.

In my project:configMAX_PRIORITIES = 2,configKERNEL_INTERRUPT_PRIORITY =7.

PINT0、PINT1 Priority =4 ;Enet Priority = 6;CTIMER0、CTIMER1 Priority = 4;

All other peripherals's interrupt are disabled.