- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- LPCマイクロコントローラ

- :

- USB_VBUS and USB1_VBUS

USB_VBUS and USB1_VBUS

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

USB_VBUS and USB1_VBUS

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

The LPC546xx datasheet says as follows.

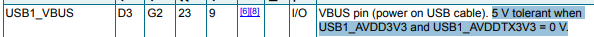

When USB1_AVDD3V3, USB1_AVDDTX3V3 and VDD are connected to 3.3V LDO, is USB1_VBUS 5V tolerant?

I have another question about VBUS, If USB1 is only used for host mode, should it be connected to VDD instead of VBUS according to table 5. termination of unused pins?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Maki,

Q1)When USB1_AVDD3V3, USB1_AVDDTX3V3 and VDD are connected to 3.3V LDO, is USB1_VBUS 5V tolerant?

>>>>>yes, the USB1_VBUS is an digital signal input pin for LPC546xx family, the USB1_VBUS 5V tolerant means that the pin can accept both 5V logic and 3.3V logic signal. When USB1_AVDD3V3, USB1_AVDDTX3V3 and VDD are connected to 3.3V LDO, USB1_VBUS is 5V tolerant.

Q2)I have another question about VBUS, If USB1 is only used for host mode, should it be connected to VDD instead of VBUS according to table 5. termination of unused pins?

>>>>>>If the USB1 is only used for host mode, and the host USB1 connector provide 5V power for the USB device which inserted into the USB1 connector, in the case, I suppose that the VDD power supply(3.3V) is from the 5V power supply via a regulator, the USB1_VBUS signal pin is not used, you can connect to either VDD or GND or float.

Pls refer to section 13.7 in data sheet.

Hope it can help you

BR

Xiangjun Rong

13.7 Suggested USB interface solutions

The USB device can be connected to the USB as self-powered device (see Figure 48) or

bus-powered device (see Figure 49).

"

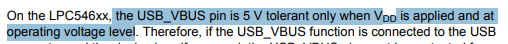

On the LPC546xx, the USB_VBUS pin is 5 V tolerant only when VDD is applied and at

operating voltage level. Therefore, if the USB_VBUS function is connected to the USB

connector and the device is self-powered, the USB_VBUS pin must be protected for

situations when VDD = 0 V.

"

PLS note above line.

If VDD is always at operating level while VBUS = 5 V, the USB_VBUS pin can be

connected directly to the VBUS pin on the USB connector.

For systems where VDD can be 0 V and VBUS is directly applied to the VBUS pin,

precautions must be taken to reduce the voltage to below 3.6 V, which is the maximum

allowable voltage on the USB_VBUS pin in this case.

One method is to use a voltage divider to connect the USB_VBUS pin to the VBUS on the

USB connector. The voltage divider ratio should be such that the USB_VBUS pin is

greater than 0.7 VDD to indicate a logic HIGH while below the 3.6 V allowable maximum

voltage.

For the following operating conditions

VBUSmax = 5.25 V

VDD = 3.6 V,

the voltage divider should provide a reduction of 3.6 V/5.25 V or ~0.686 V.