- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- LPCマイクロコントローラ

- :

- Trouble Reading/Writing data on external SPI flash W25Q80DV on LPC54016

Trouble Reading/Writing data on external SPI flash W25Q80DV on LPC54016

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I am using "spifi_polling_transfer" sdk example on a custom board for lpc54016 with winbond w25Q80DV.

I have few beginners questions,

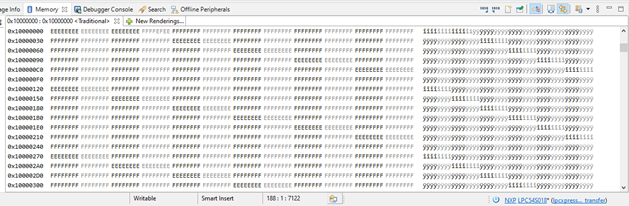

1. How can I view the data for external SPI Flash on MCUxpresso IDE 11.5.0? I tried using "memory tab" not sure if that's the RAM or External SPI flash.

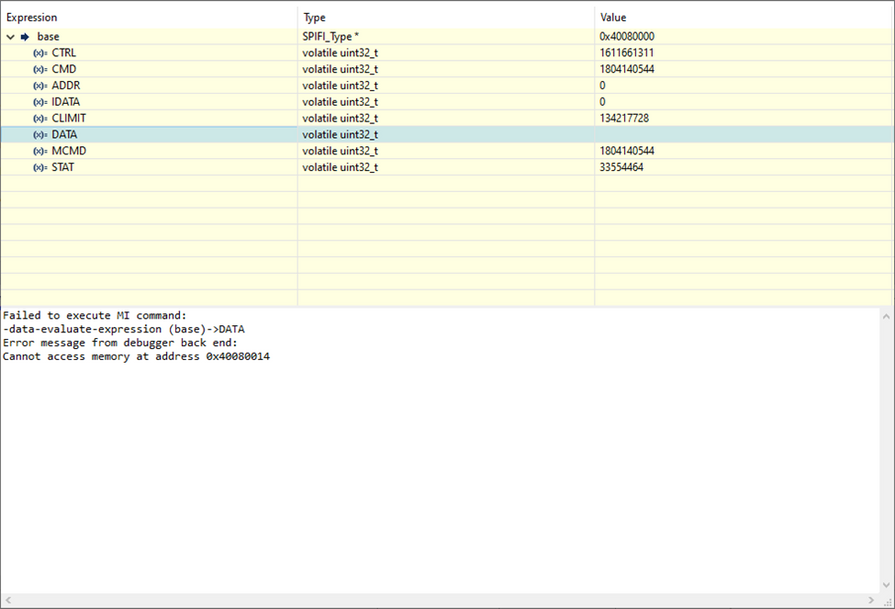

2. The base address defined is, 0x40080000u.

/** Peripheral SPIFI0 base address */

#define SPIFI0_BASE (0x40080000u)

Does that means this is the address we start writing the data?

3. The start address defines is (0x10000000)

#define FSL_FEATURE_SPIFI_START_ADDR (0x10000000)

This is where we read the data we wrote, why does this address not match with SPIFI0 base address?

4. where I fill the buffer

/* Set the buffer */

for (i = 0; i < PAGE_SIZE; i++)

{

g_buffer[i] = i;

}

5. I am using the sample sdk example as it is, do I need to change anything? the sample code used W25Q128JV.

I am trying to use the external flash to store the code memory as well as store some data.

the location where this data is written is always 0x20000048. Why is that? Is this the RAM location or external SPI flash.

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I was finally able to read and write w25q80dv chip using sample code for w25q128 "SPIFI polling transfer".

I reduced the frequency to 12Mhz, change the configuration to,

/* SPIFI Descriptor - W25Q80DVSIG */

(void (*)(void))0x00000000, // 0xFFFFFFFF to default 1-bit SPI mode ;DevStrAdr

(void (*)(void))0x001440EF, // mfgId + extCount for W25Q80DV

(void (*)(void))0x00000000, // extid 0-3

(void (*)(void))0x00000000, // reserved

(void (*)(void))0x1301001D, // caps

(void (*)(void))0x0000000F, // Blks + RESV1 for W25Q80DV

(void (*)(void))0x00010000, // blkSize

(void (*)(void))0x00000000, // reserved

(void (*)(void))0x00000100, // pageSize + RESV2

(void (*)(void))0x00003F00, // maxReadSize

(void (*)(void))0x68506850, // maxClkRate,maxReadRate,maxHSReadRate,maxProgramRate

(void (*)(void))0x04030050, // maxHSProgramRate,initDeInitFxId,clearStatusFxId,getStatusFxId,

(void (*)(void))0x14110D09, // setStatusFxId,setOptionsFxId,getReadCmdFxId,getWriteCmdFxId

#endif

and I had to give 16 data clock pulse after 8 clock pulse for write status register(01h). 6 clock pulse are for register 1 & register 2.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I was finally able to read and write w25q80dv chip using sample code for w25q128 "SPIFI polling transfer".

I reduced the frequency to 12Mhz, change the configuration to,

/* SPIFI Descriptor - W25Q80DVSIG */

(void (*)(void))0x00000000, // 0xFFFFFFFF to default 1-bit SPI mode ;DevStrAdr

(void (*)(void))0x001440EF, // mfgId + extCount for W25Q80DV

(void (*)(void))0x00000000, // extid 0-3

(void (*)(void))0x00000000, // reserved

(void (*)(void))0x1301001D, // caps

(void (*)(void))0x0000000F, // Blks + RESV1 for W25Q80DV

(void (*)(void))0x00010000, // blkSize

(void (*)(void))0x00000000, // reserved

(void (*)(void))0x00000100, // pageSize + RESV2

(void (*)(void))0x00003F00, // maxReadSize

(void (*)(void))0x68506850, // maxClkRate,maxReadRate,maxHSReadRate,maxProgramRate

(void (*)(void))0x04030050, // maxHSProgramRate,initDeInitFxId,clearStatusFxId,getStatusFxId,

(void (*)(void))0x14110D09, // setStatusFxId,setOptionsFxId,getReadCmdFxId,getWriteCmdFxId

#endif

and I had to give 16 data clock pulse after 8 clock pulse for write status register(01h). 6 clock pulse are for register 1 & register 2.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

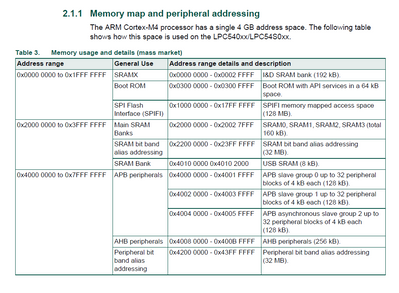

Pls refer to the memory map of LPC546xx in UM11060.pdf, as you see that the base address 0x1000_0000 is spifi flash start address, the 0x2000_0000 is on-chip RAM address, the 0x4000_0000 is peripheral register address.

Hope it can help you

BR

XiangJun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I am really struggling with reading/writing ext spi flash. Any help would be really appreciated.

I don't understand if I can read and write the same code "SPIFI polling transfer" on EVK board with 54S018 and W25Q128. Why can't I use the same software with 54016 with w25q80DV.

I reduced the frequency to 12Mhz, changed the configuration setting as per w25q80. Not sure what else I need to do.

Are there any hardware requirements?

How does the sample code checks if the JEDEC ID is correct?

This is the config I am using,

/* SPIFI Descriptor - W25Q80DVSIG */

(void (*)(void))0x00000000, // 0xFFFFFFFF to default 1-bit SPI mode ;DevStrAdr

(void (*)(void))0x001440EF, // mfgId + extCount for W25Q80DV

(void (*)(void))0x00000000, // extid 0-3

(void (*)(void))0x00000000, // reserved

(void (*)(void))0x1301001D, // caps

(void (*)(void))0x0000000F, // Blks + RESV1 for W25Q80DV

(void (*)(void))0x00010000, // blkSize

(void (*)(void))0x00000000, // reserved

(void (*)(void))0x00000100, // pageSize + RESV2

(void (*)(void))0x00003F00, // maxReadSize

(void (*)(void))0x68506850, // maxClkRate,maxReadRate,maxHSReadRate,maxProgramRate

(void (*)(void))0x04030050, // maxHSProgramRate,initDeInitFxId,clearStatusFxId,getStatusFxId,

(void (*)(void))0x14110D09, // setStatusFxId,setOptionsFxId,getReadCmdFxId,getWriteCmdFxId

#endif

Tried to use the chip as dual and quad mode, but still no luck.

There are not many post talking about communication with external SPI flash.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

So if I want to write some data in external SPI flash it should be written starting from 0x4000_0000?

Is there a reason why I am getting an error while writing the data buffer and I get that "Failed to execute MI command"? It says cannot access at address 0x40080014 because I have "??" there.

This is what I have set in the code,

/** Peripheral SPIFI0 base address */

#define SPIFI0_BASE (0x40080000u)

This is where I write all the data and command.

/* @brief SPIFI start address */

#define FSL_FEATURE_SPIFI_START_ADDR (0x10000000)

uint8_t *val = (uint8_t *)FSL_FEATURE_SPIFI_START_ADDR;

This is where I read the written data.

I am using the sdk example "SPIFI polling transfer" as it is.

It would be really helpful if you tell me if I am not doing anything right in these definitions or I need to use a different sdk example.

Thank you!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I have to say that the address 0x4000_0000 are peripheral register address, they have special meaning for each register, you can NOT write them as general memory.

For the spifi flash writing example project "spifi_polling_transfer",

/* Write enable */

SPIFI_SetCommand(EXAMPLE_SPIFI, &command[WRITE_ENABLE]);

/* Set address */

SPIFI_SetCommandAddress(EXAMPLE_SPIFI, 0U);

//Rong write:

the address 0 is the external spifi flash offset, it's absolute address is 0x1000_0000 in the ARM core address space, which also save application code, so if your write address, the application code is overwritten. You have to select an offset which does not occupy with application code so that you can put your application data to the space.

For the program part code, it is the same that the address is the offset of external flash rather than absolute address.

/* Erase sector */

SPIFI_SetCommand(EXAMPLE_SPIFI, &command[ERASE_SECTOR]);

/* Check if finished */

check_if_finish();

Hope it can help you

BR

XiangJun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I tried to run the ""spifi_polling_transfer"" code on EVK 540s0xx board and it works perfect.

Not sure why it does work on my custom board with controller LPC54016 and the winbond I am using is W25Q80DV.

I am able to read the memory and erase it successfully but when I try to write it, it writes from 0x10000000 to 0x17FFFFFF location.

I tried to check the frequency of SPIFI, by

spifiFreq = CLOCK_GetSpifiClkFreq();

and it is 96Mhz. Not sure if it is the configuration?

#ifdef W25Q128JVFM

/* SPIFI Descriptor - W25Q128JVFM */

(void (*)(void))0x00000000, // 0xFFFFFFFF to default 1-bit SPI mode ;DevStrAdr

(void (*)(void))0x001870EF, // mfgId + extCount

(void (*)(void))0x00000000, // extid 0-3

(void (*)(void))0x00000000, // reserved

(void (*)(void))0x1301001D, // caps

(void (*)(void))0x00000100, // Blks + RESV1

(void (*)(void))0x00010000, // blkSize

(void (*)(void))0x00000000, // reserved

(void (*)(void))0x00000100, // pageSize + RESV2

(void (*)(void))0x00003F00, // maxReadSize

(void (*)(void))0x68506850, // maxClkRate,maxReadRate,maxHSReadRate,maxProgramRate

(void (*)(void))0x04030050, // maxHSProgramRate,initDeInitFxId,clearStatusFxId,getStatusFxId,

(void (*)(void))0x14110D09, // setStatusFxId,setOptionsFxId,getReadCmdFxId,getWriteCmdFxId

#endif

Do I need to change anything here?

If I am able to erase and read then I think the configuration is correct. Not sure what's going wrong with the write operation.

Also I changed the Program page command from 31H to 01H according to the W25Q80 datasheet

//{1, false, kSPIFI_DataOutput, 0, kSPIFI_CommandAllSerial, kSPIFI_CommandOpcodeOnly, 0x31}};

{1, false, kSPIFI_DataOutput, 0, kSPIFI_CommandAllSerial, kSPIFI_CommandOpcodeOnly, 0x01}};

Any help will be appreciated.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I changed some of the configuration settings accoding to the datasheet for w25q80dv,

(void (*)(void))0x001440EF, // mfgId + extCount for W25Q80DV

(void (*)(void))0x0000000F, // Blks + RESV1 for W25Q80DV

I reduced the frequency to 49Mhz, 24Mhz still the garbage value is written in the flash W25Q80DV.

Works perfect on EVK56S0xx board. Attach the zip file for my code.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

static inline void CLOCK_EnableClock(clock_ip_name_t clk)

{

uint32_t index = CLK_GATE_ABSTRACT_REG_OFFSET(clk);

if (index < 3UL)

{

SYSCON->AHBCLKCTRLSET[index] = (1UL << CLK_GATE_ABSTRACT_BITS_SHIFT(clk));

}

else

{

SYSCON->ASYNCAPBCTRL = SYSCON_ASYNCAPBCTRL_ENABLE(1);

ASYNC_SYSCON->ASYNCAPBCLKCTRLSET = (1UL << CLK_GATE_ABSTRACT_BITS_SHIFT(clk));

}

}

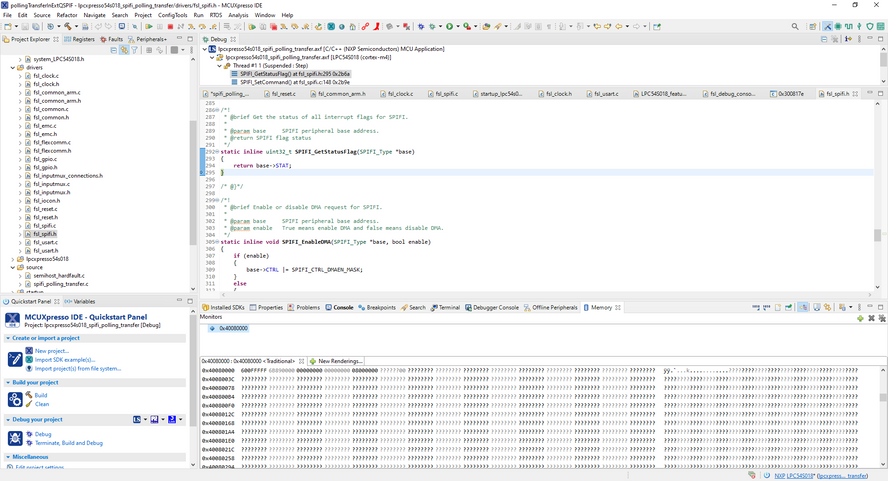

I tried to debug exactly where I get question marks at 40080000 location and it looks like, when I execute this line "SYSCON->AHBCLKCTRLSET[index] = (1UL << CLK_GATE_ABSTRACT_BITS_SHIFT(clk));".

I have a 12Mhz crystal on my board, do I need to make some changes in the sample sdk code?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I tried to debug, I think due to some reason my data is not getting written,

this is what I'm getting.

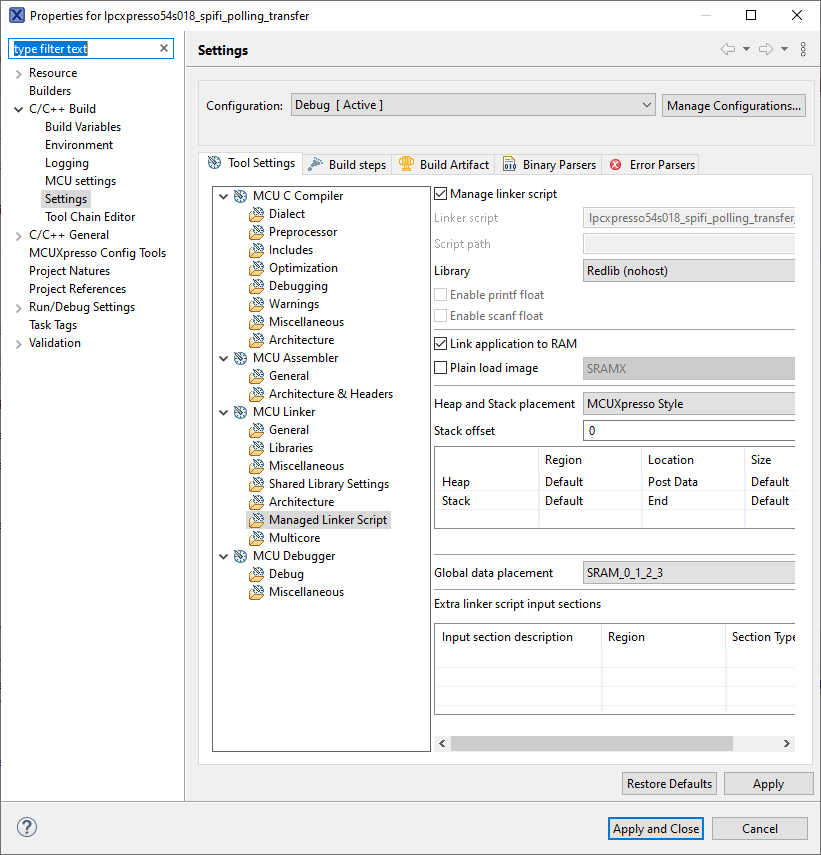

some screen shots if that's going to help understand my problem,