- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- Re: SSP Slave Mode Not Working in LPC11u68

SSP Slave Mode Not Working in LPC11u68

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

SSP Slave Mode Not Working in LPC11u68

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We are using SSP0 as in slave mode. But the example given in LPC Expresso is not working in slave mode. In slave mode it is not receiving any data. It is in busy mode. Not able to understand the behaviour. I have check it in master mode in order to confirm the clock and pin configuration with LPC43XX SPI .

Following are the modes in which the communication is successful.

1) In Master Mode: LPC11E67 (SSP) in master mode , 8 bit data bus, Mode 0, clock 1MHz. LPC4367 (SPI) in slave mode , , 8 bit data bus, Mode 2, clock 1MHz

Here we are able to communicate and the data is receiving properly in LPC11E67

2) In Slave Mode: LPC11E67 (SSP) in Slave mode , 8 bit data bus, Mode 0, clock 1MHz. LPC4367 (SPI) in Master mode , , 8 bit data bus, Mode 2, clock 1MHz

Here in this case we are not receiving any data in slave side (LPC11E67) Referred all the forum not able to get any proper solution in data sheet and through forums.

Tried all the inputs from the forums but still the result is same. It always remains in the Busy status and data is 0.

Kindly provide the working and tested code of LPC11E67 SPP0/1 in slave mode

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Gaurav More,

Now, after testing it today(this really time-consuming ), I can make the LPC4367 SPI master work, just copy your SPI code to my side, please check the details.

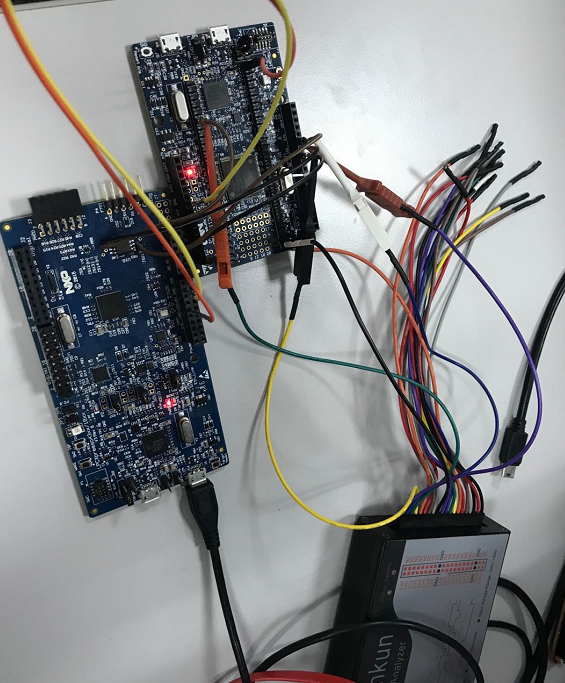

1. Hardware

SPI master: LPC4367 or LPC43S67, use the lpcxpress board.

SPI slave : LPC11U68, use the LPCXpresso board'

1)LPC4367 SPI pin

SPI_CLK : P3_3

SPI_MISO : P3_6

SPI_MOSI : P3_7

SPI_SSEL : P3_8, GPIO control

Note, if you use the lpcxpresso LPC4367 board, remove JS23, just disconnect it from the external flash.

2)LPC11U68

SPI_CLK : P1_29

SPI_MISO : P0_8

SPI_MOSI : P0_9

SPI_SSEL : P0_2,

Connections:

2. Software IDE

LPCXpresso v8.2.2 build650, MCUXpresso IDE also Ok.

3. Software code

Based on the LPCopen code for LPC4367 and LPC11U68

Please check my attached code for both LPC4367 and LPC11U68

If you find the LPC4367 code project is ssp,don't worry, I already delete the whole code, and use the SPI module, copy it from your code.

But I modify the transfer and receive code:

uint16_t SPI_Data_Transfer_kerry(uint16_t dummy_data,uint16_t timeout)

{

uint16_t read_data;

uint16_t Count =0;

enable_SPI_SS();

Chip_SPI_Int_FlushData(LPC_SPI); ///* Clear status */

Chip_SPI_SendFrame(LPC_SPI,dummy_data);

while((!(Chip_SPI_GetStatus(LPC_SPI) & SPI_SR_SPIF)));

read_data = Chip_SPI_ReceiveFrame(LPC_SPI);

disable_SPI_SS();

return read_data;

}I didn't add the delay, but I add clear status code.

I find your LPC11U68 have a lot of problem, you configure the as 8bit, not 16 bits, but your LPC4367 use the 16bits, so I use my own LPC11U68 code directly ,but send the same data as your LPC11U68.

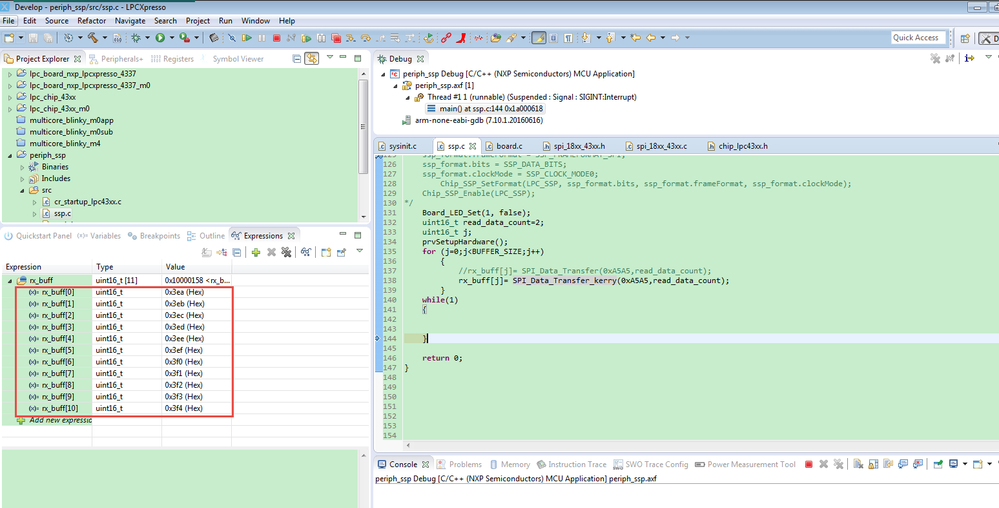

4. Test result

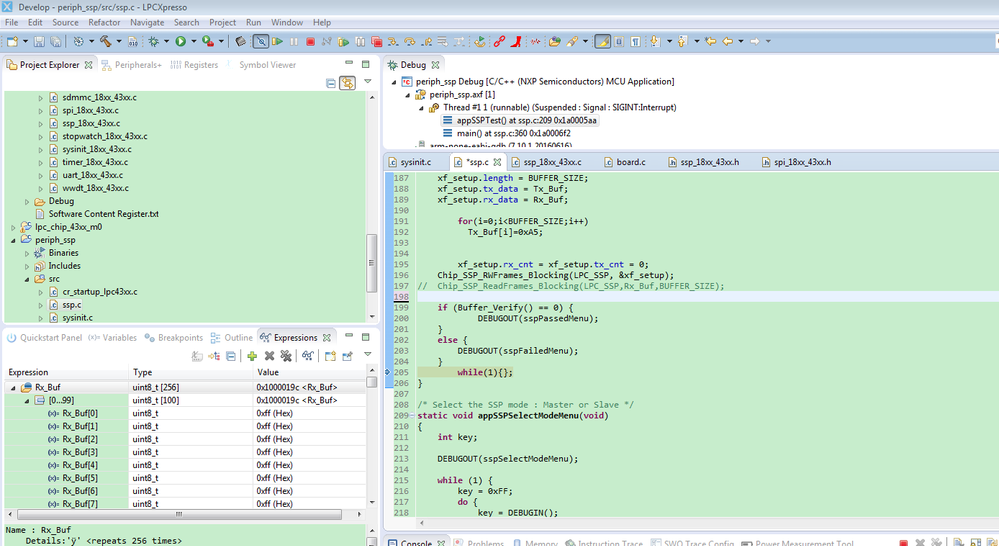

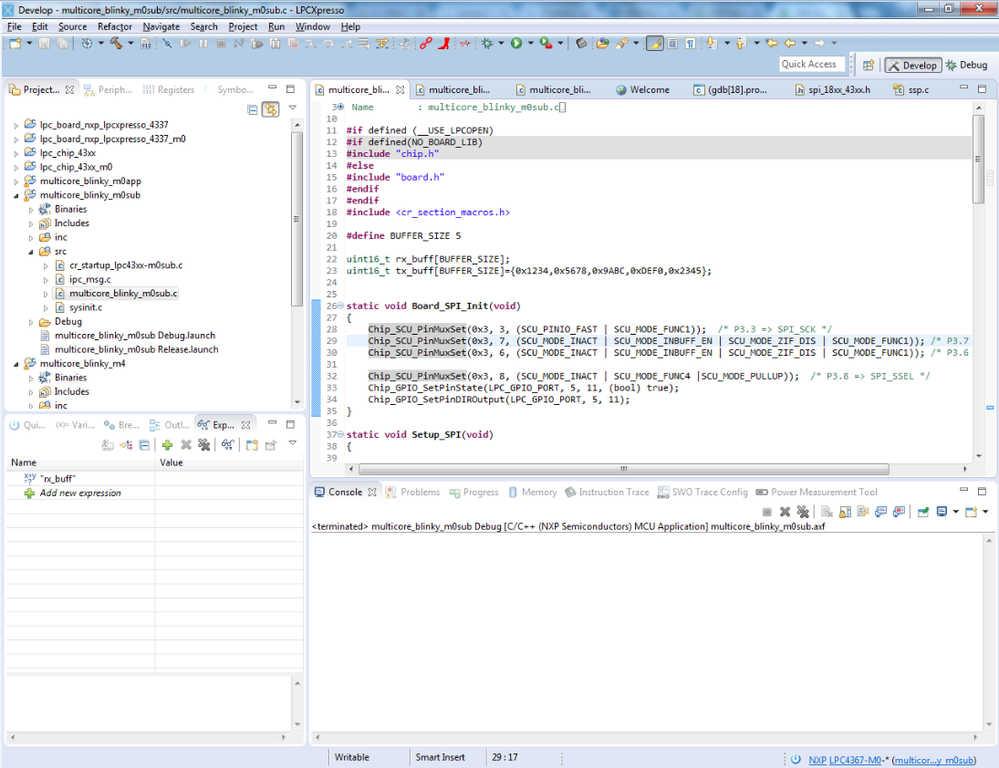

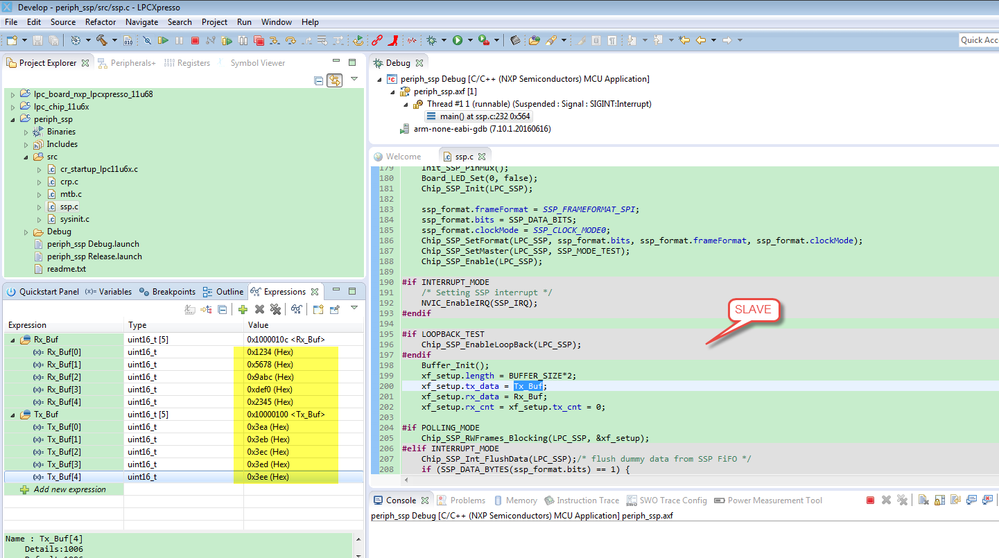

1)LPC11U68 debug code

You can find the LPC11U68 slave can receive all the 0XA5a5 from the master side.

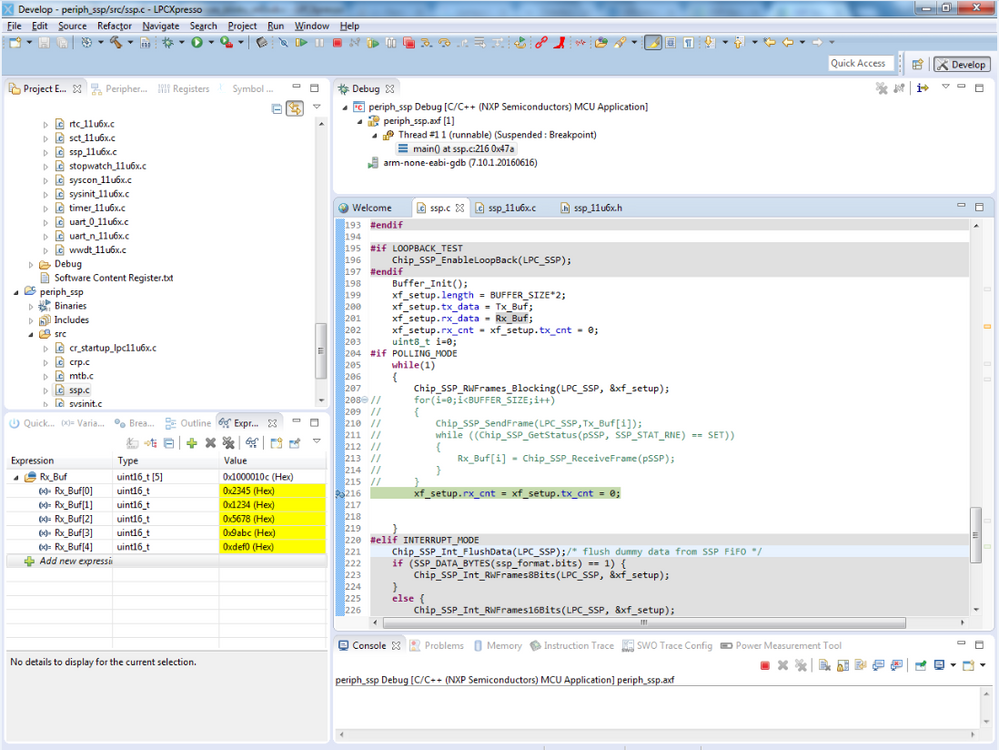

2)LPC4367 debug code

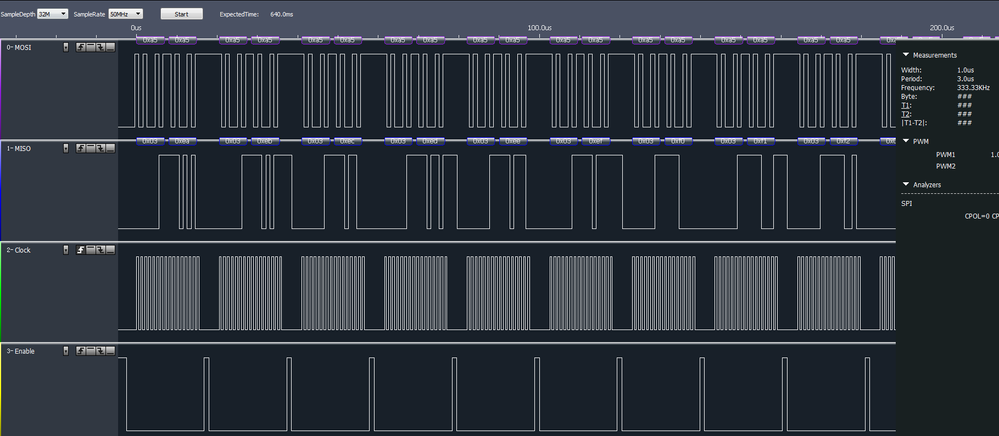

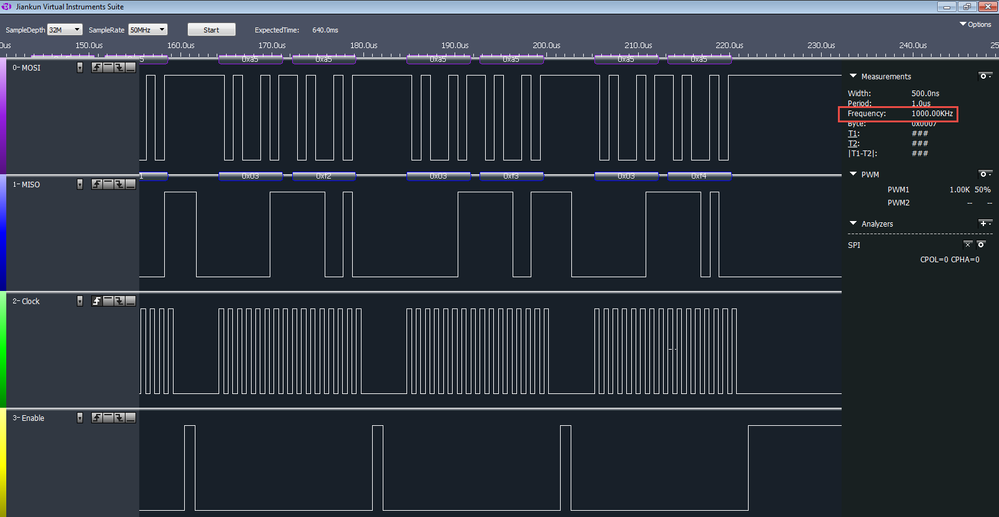

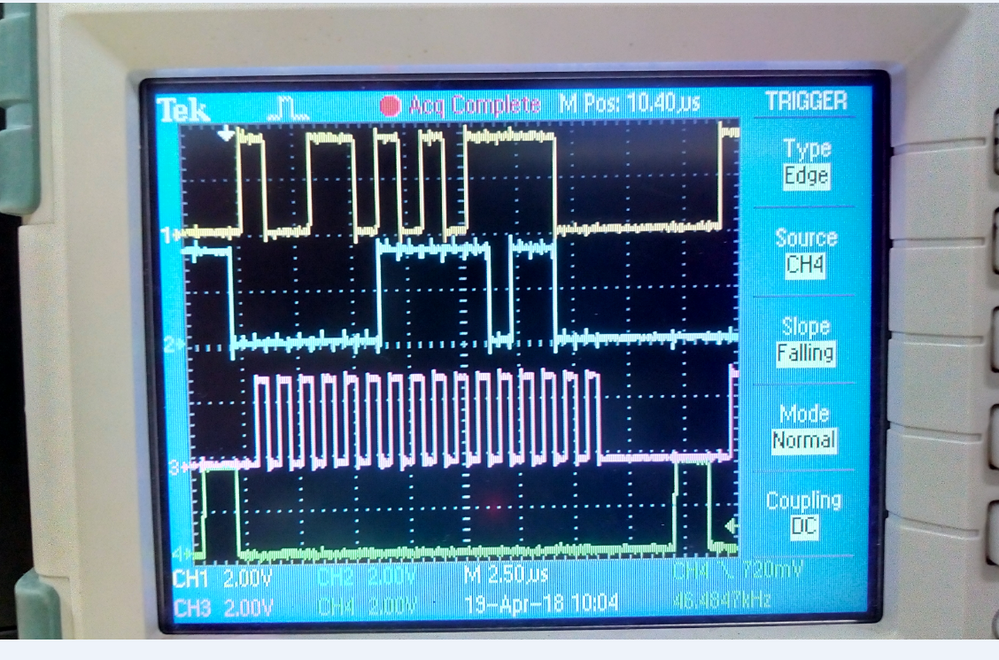

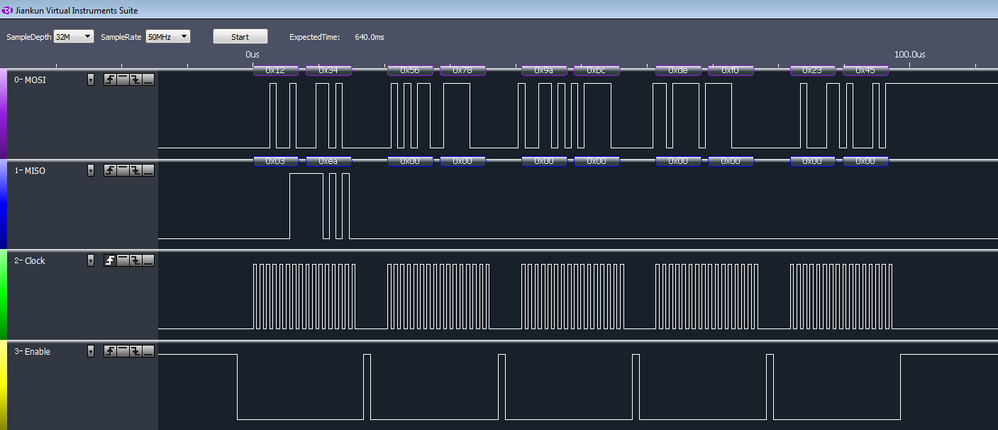

3) SPI bus wave

From 2) and 3), you can find the master also can receive all the correct data from the LPC11U68, I didn't add the delay which you mentioned.

The SPI baudrate is 1Mhz.

So, if you still not OK, please use my attached two projects, master and slave, then test it again.

Wish it helps you!

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your interest in NXP LPC product, I would like to provide service for you.

Two points need you to check at first:

1. Keep the master and slave in the same mode

Customer's master and slave mode is not the same, please change it to the same mode at first.

2. Test the SPI wave then send it to me.

Please use the logic analyzer or the 4 channel oscilloscope to test the SPI bus wave: SPI_CS, SPI_CLK, SPI_MOSI, SPI_MISO.

Check the wave, whether the SPI bus wave is correct to the slave? It's very important.

After test, please send me the SPI wave with problems.

If the problem still exist, please tell me the detail code which you are using, you can send me the problem master and slave code, I will test it on my side.

Please check these points at first.

Then give me the updated information.

Waiting for your reply!

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Kerry,

Considering your inputs mentioned above i made changes in the code and made both master and Slave device to same mode (Mode 0). Here the master device is LPC4367 and Slave is LPC11u68. Rest all the configuration are unchanged. But still i got the same result. I am not able to receive any data at the slave side.

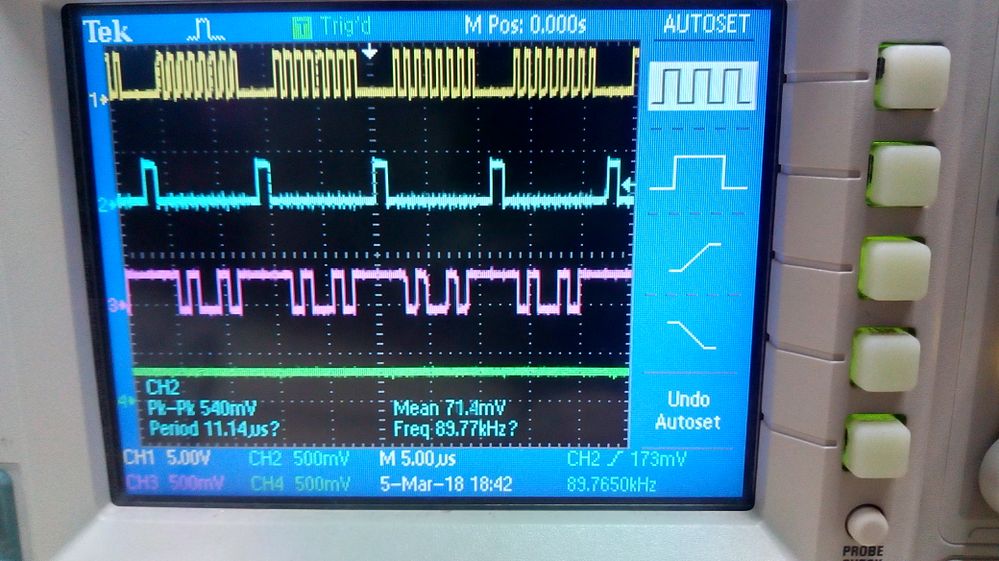

Considering the 2nd input please find attached wave forms for your reference. Here the yellow line is for SCLK, Blue is for SSEL, pink one is for DATA (MOSI) and Green is (MISO). The data transferred is 0XA5 from master to slave and slave is suppose to send 0x55 but you can see that there is not output from salve.

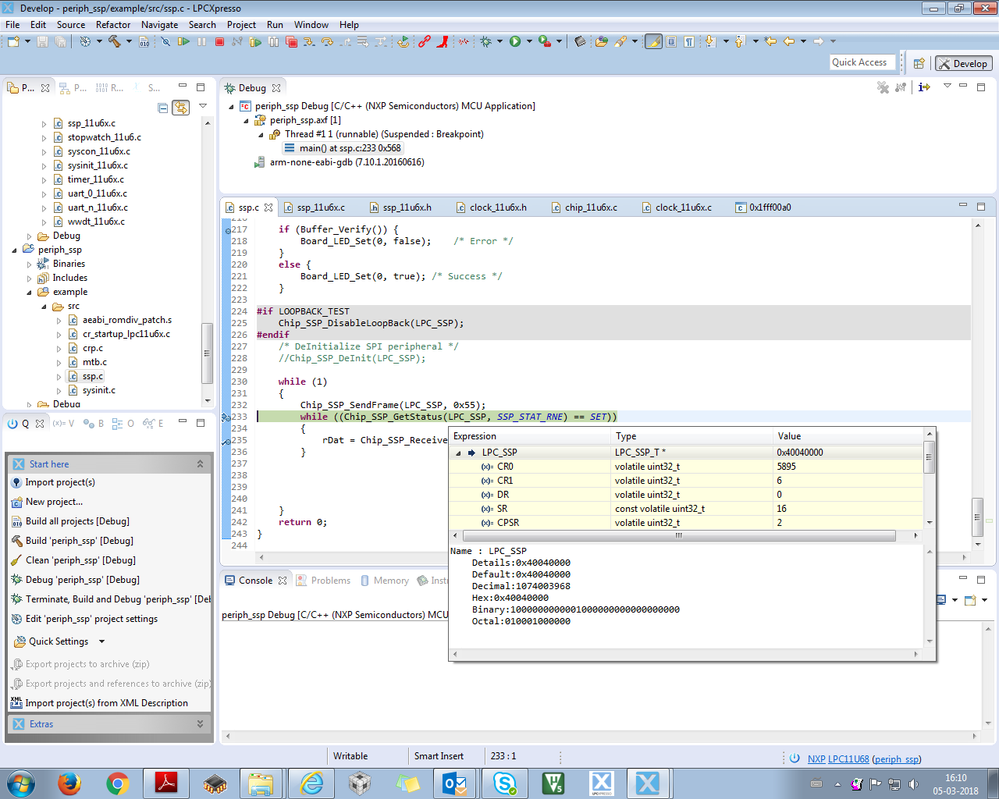

I have also attached the screens shot of the status of the slave register and you can see that SR value is 16. it remains in the same manner.

Regarding the Code please find the details of the code mentioned below

System freq is 48MHz

Pin Mux Section for LPCExpresso Board:

Chip_IOCON_PinMuxSet(LPC_IOCON, 1, 29,(IOCON_FUNC1 | IOCON_MODE_INACT));

Chip_IOCON_PinMuxSet(LPC_IOCON, 0, 8,(IOCON_FUNC1 | IOCON_MODE_INACT));

Chip_IOCON_PinMuxSet(LPC_IOCON, 0, 9,(IOCON_FUNC1 | IOCON_MODE_INACT));

Chip_IOCON_PinMuxSet(LPC_IOCON, 0, 2,(IOCON_FUNC1 | IOCON_MODE_INACT));

// Chip_IOCON_PinMuxSet(LPC_IOCON, 0, 2,(IOCON_FUNC0 | IOCON_MODE_INACT));

SSP 0 Init Function :

pSSP = LPC_SSP0;

Chip_Clock_EnablePeriphClock(Chip_SSP_GetClockIndex(pSSP));

Chip_SSP_SetSSPClkDivider(pSSP, 1);

Chip_SYSCTL_PeriphReset(Chip_SSP_GetResetIndex(pSSP));

Chip_SSP_Set_Mode(pSSP, SSP_MODE_SLAVE);

Chip_SSP_SetFormat(pSSP, SSP_BITS_8, SSP_FRAMEFORMAT_SPI, SSP_CLOCK_MODE0);//SSP_CLOCK_CPHA0_CPOL0

Chip_SSP_SetBitRate(pSSP, 1000000);

Chip_SSP_Enable(pSSP);

while (1)

{

Chip_SSP_SendFrame(pSSP, 0x55);

while ((Chip_SSP_GetStatus(pSSP, SSP_STAT_RNE) == SET))

{

rDat = Chip_SSP_ReceiveFrame(pSSP);

}

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

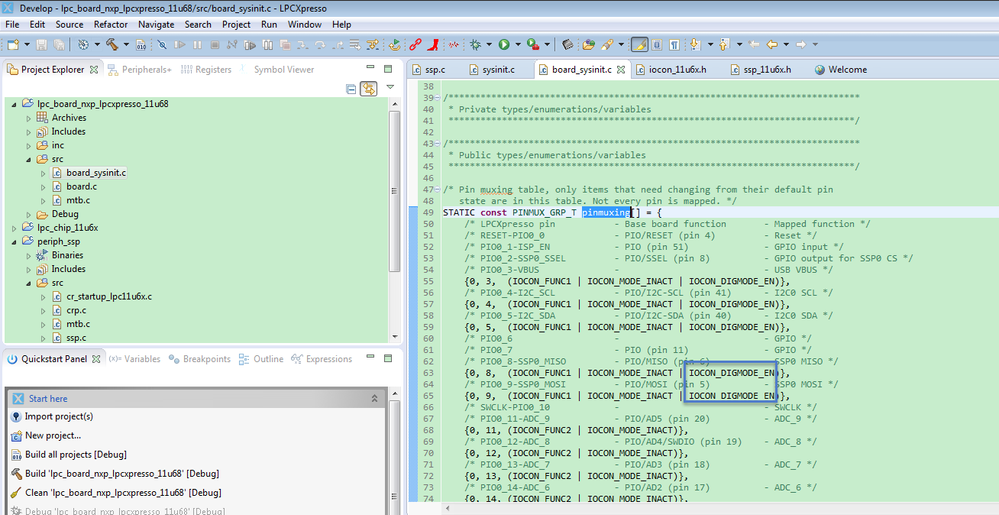

Hi Gaurav More,

I have tested your code on my side, and debug the register, now it works OK on my side.

One point need to do the modification:

static void Init_SSP_PinMux(void)

{

#if (LOOPBACK_TEST == 0)

#if defined(BOARD_MANLEY_11U68)

#warning "No SSP setup defined"

#elif defined(BOARD_NXP_LPCXPRESSO_11U68)

//#warning "No SSP setup defined"

/*

Chip_IOCON_PinMuxSet(LPC_IOCON, 1, 29,(IOCON_FUNC1 | IOCON_MODE_INACT));

Chip_IOCON_PinMuxSet(LPC_IOCON, 0, 8,(IOCON_FUNC1 | IOCON_MODE_INACT));

Chip_IOCON_PinMuxSet(LPC_IOCON, 0, 9,(IOCON_FUNC1 | IOCON_MODE_INACT));

Chip_IOCON_PinMuxSet(LPC_IOCON, 0, 2,(IOCON_FUNC1 | IOCON_MODE_INACT));

// Chip_IOCON_PinMuxSet(LPC_IOCON, 0, 2,(IOCON_FUNC0 | IOCON_MODE_INACT));

// Chip_GPIO_SetPinDIROutput(LPC_GPIO, 0, 2 );

*/

Chip_IOCON_PinMuxSet(LPC_IOCON, 1, 29,(IOCON_FUNC1 | IOCON_MODE_INACT| IOCON_DIGMODE_EN));

Chip_IOCON_PinMuxSet(LPC_IOCON, 0, 8,(IOCON_FUNC1 | IOCON_MODE_INACT| IOCON_DIGMODE_EN));

Chip_IOCON_PinMuxSet(LPC_IOCON, 0, 9,(IOCON_FUNC1 | IOCON_MODE_INACT| IOCON_DIGMODE_EN));

Chip_IOCON_PinMuxSet(LPC_IOCON, 0, 2,(IOCON_FUNC1 | IOCON_MODE_INACT| IOCON_DIGMODE_EN));

#else

#error "No SSP setup defined"

#endif

#endif

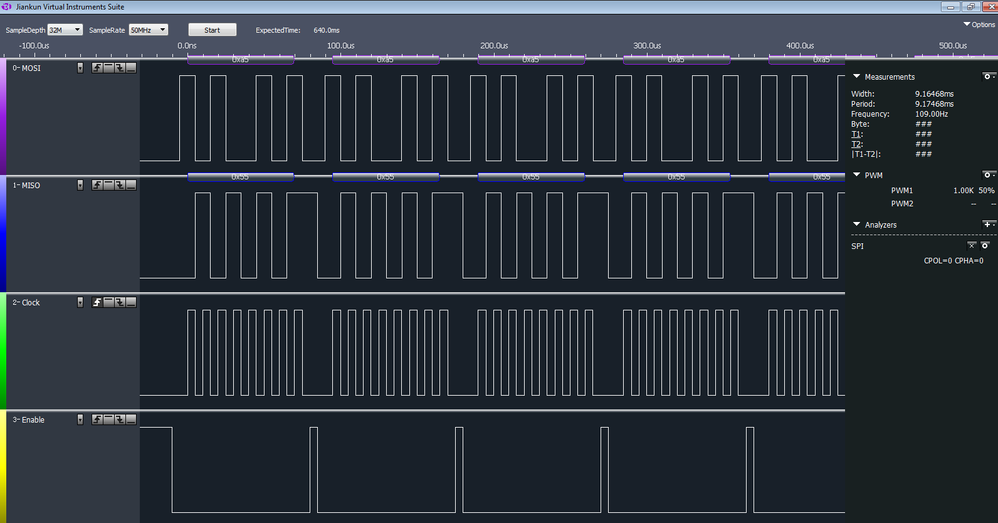

}This is the test SPI bus wave:

You can find the MISO send out the 0X55 which is your needed data.

I also attached my modified project for your reference.

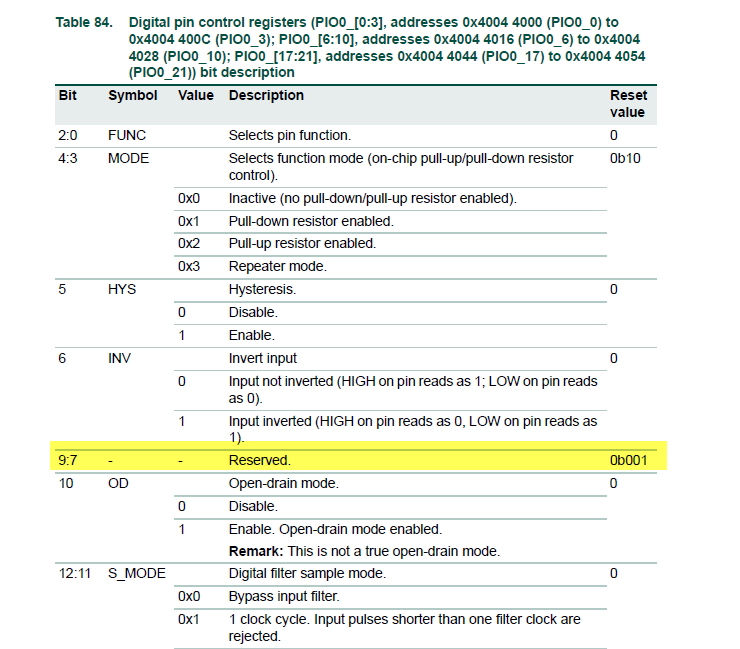

Your original configuration will make bit9:7 to 0, that's why your SPI slave can't work.

Wish it helps you!

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kerry, Could you let me know the sw Jiankun Virtual instruments which you use to capture SPI signal .

is it a free software? and i'm curious whether can use it for debugging purpose or not ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Hau Lam,

Jiankun is just the logic analyzer attached PC software, it is not the general instruments.

When you buy the logic analyzer, you will get the according software.

Wish it helps you!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kerry,

Awaiting for your response sicne it will help me to improve the performance of the system. Also let me know if any more details are required.

Thanks

Gaurav More

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Gaurav,

Now, I use LPC4357 as master, LPC11U68 as slave, I can reproduce your mentioned problem if I use the lpcopen API Chip_SSP_RWFrames_Blocking directly.

MISO have 0X55 data, but the buff still 0XFF.

I will do the deep research, any updated information on my side, will let you know!

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kerry,

I have checked the code also which i had sent you . There is a problem with that code so i have modified and checked from my side . Consider the attached code for your processing and reference. Modification in that code is done with respect to the sysinit function where the peripheral clock was not enable and in SSP Init where bit format is changed from 8 bit to 16 bit. I have tested the code from my side and I have taken the snap shot of the observation and the waveforms of SPI Communication.

Please find below the waveform of with Delay and the data received with Delay or Timeout.

Waveform Details Yellow = MOSI, Blue = MISO, Pink = Clock, Green = SSEL

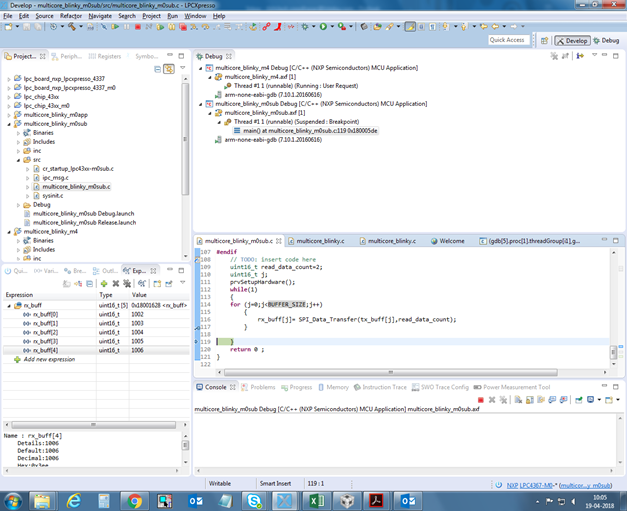

You can see that the data received is 1002,1003, 1004,1005,1006 and also find attached Waveform with Delay and Data received Without Delay.

Here You can see the data is lost and 0 is received in between 1002,0,0 ,1005,1006.

Kindly go through the code and update the details accordingly.

We have check with tyour code that you have sent but but it that we did modification in master side by adding sequence of data to be sent by master to slave as mentioned below in tx buffer ,

uint16_t tx_buff[BUFFER_SIZE]={0x1234,0x5678,0x9ABC,0xDEF0,0x2345};

AS a response we are recieving wrong sequence to slave even though we are recieving correct sequence in master. see the screen shot below,

You can see that the sequence is not matching. So i request you to check it with our code of SSP since i think it is not yet resolved and the data is still not matching. Even after adding clear status line.

You can test the coe with doing the above mentioned modification and calling the polling method in while in master side and then verify.

Waiting for your response. And one omer think can we have the process that if i am responding it should reach you immediately since everey time moderators are reviwing and then you are recieving the response. What is happeing i am sending you response butyou will reciev very let and due to that there will not be any syncing in the post at at all.

Request you to let me know if i can g with some other way to respond you faster.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Gaurav More,

I have tested your newest slave code, this code still have problems, this is the SPI bus wave:

Your LPC11U68 slave MISO didn't send out the correct data.

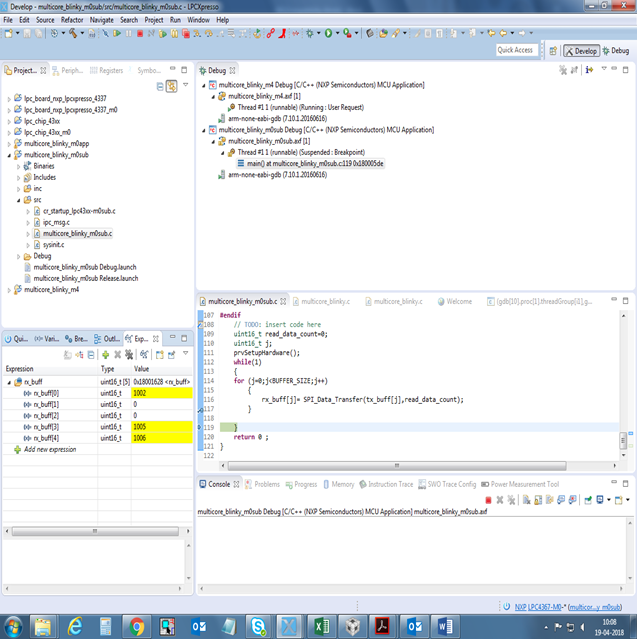

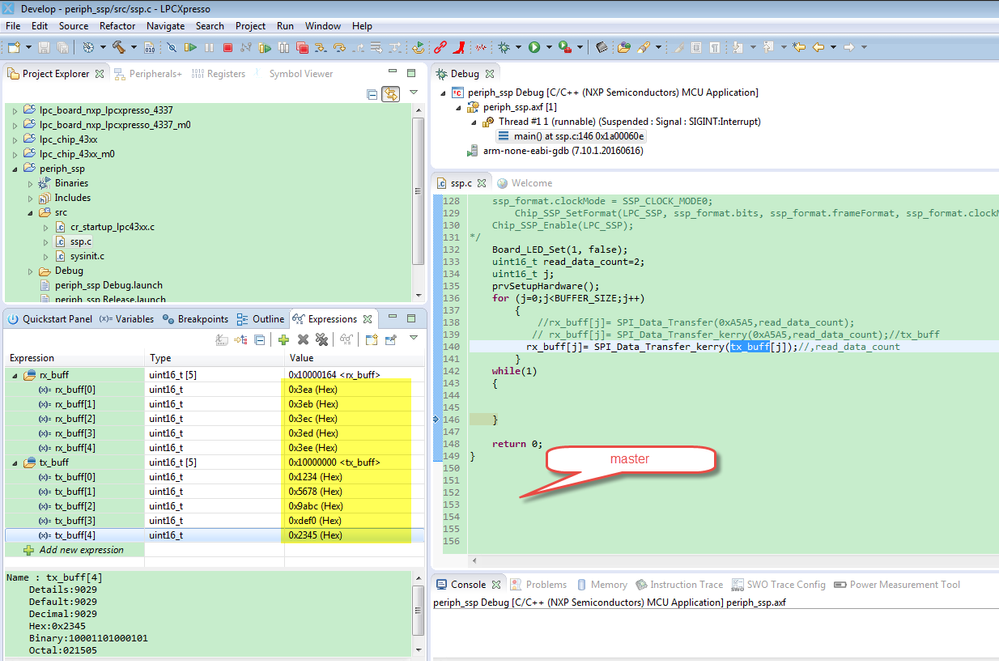

It seems you didn't test both my SPI master(LPC43S67) and slave code(LPC11U68), this is my test result with the modified master and slave:

1. SPI BUS wave

You can find both mosi and miso in the SPI bus wave is correct, which you need is:

LPC43S67 Master

Send: 0X1234, 0X5678,0X9ABC, 0XDEF0, 0X2345

Receive: 0X3ea, 0x3eb, 0x3ec,0x3ed,0x3ee

LPC11U68 Slave

Send: 0X3ea, 0x3eb, 0x3ec,0x3ed,0x3ee

Receive: 0X1234, 0X5678,0X9ABC, 0XDEF0, 0X2345

2. Master LPC43S67 debug result:

You can find both receive and transfer data is correct

3, Slave LPC11U68 debug result

You can find the slave both send and receive data is correct.

Actually, I just modify the Master send data to 0X1234, 0X5678,0X9ABC, 0XDEF0, 0X2345

So, I highly suggest you test both my master and slave in pair.

I attached the newest master and slave code for you reference .

I think, now, your slave code may still have problems, because the MISO don't have the correct data.

Actually, I use the same SPI pin as your code, so you just need to download may code to your board, you even don't need to modify the hardware, just check the data.

I can make sure my code works as your expect.

Please test it, thank you,

Any updated problem, just let me know!

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Gaurav More,

Thank you for your information.

Please check my above reply to you, I find you configure both LPC11U68 and LPC4357 as the SPI master, please tell me the clear information, what's the indeed SPI master you want to be?

Waiting for your confirmation.

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kerry,

Sorry mistake is from my side. I checked the code and need to modify the code from SPI Master to Slave for LPC11U68 ,rest all will remain same. the problem is that i need to put delay while reading the data at LPC4367 side as mentione in the earlier post

Enable_CT_SS();

Chip_SPI_SendFrame(LPC_SPI,Tx_data);

while(!(Chip_SPI_GetStatus(LPC_SPI) & SPI_SR_SPIF)||(ul16_Timeout_count++ < timeout));

ul16_RxData = Chip_SPI_ReceiveFrame(LPC_SPI);

Disable_CT_SS();

I do not have to put the delay in Slave side. Delay is on the master side. If the delay is not there at the master side the master will recieve 0 and as per the code mentioned above it disabled the CS. due to which the slave remains in busy mode.

This modification of including the delay is done going through one of the post mentioned related to SPI communication that, delay is required if the two controllers are of different frequency, but we need the confirmation from your side regarding the same. Either delay is required and there is another work around solution, Since it was just an article in electronics.stackexchange.com. https://electronics.stackexchange.com/questions/81107/how-to-code-spi-slaves

Other detials mention below are ok.

LPC11U68:

Controller freq: 48Mhz, SSP Clock Rate: 1Mhz, Slave Mode , Mode 0

LPC4367:

Controller freq: 100Mhz, SPI Clock Rate: 1Mhz, Master Mode, Mode , Mode 0, SPI peripheral freq: 50Mhz

Also let me know if any more details reauired

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Kerry,

Thanks a lot for for providing the solution. I cannot find the difference since the details regarding the configuration is not mentioned in the data sheet as you can see that those bits are reserved and so did not made any modifications. Request you to please provide this information in the user manual. It will help us in configuring the same.

The latest datasheet which I referred is of Rev 1.8, 19 December 2016.

Since these bits are reserved it is possible that user may not change that bit and attempt to change it. I have check the code that you have sent and compiled it . It is working fine. Further more testing will be continued and will reply you if in case any issue is there . But thank you very much, :-)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

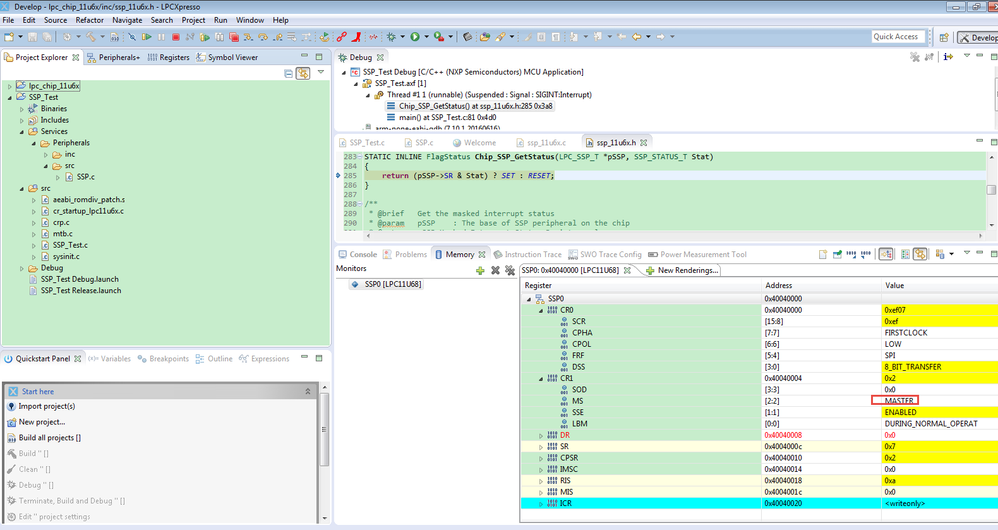

Hi Gaurav More,

That's very good to hear you also make it works with this workaround.

Yes, the user manual really didn't add the note about this point, but normally, if the register reserved area have the default data, please keep that default data, don't modify it.

Actually, in the lpcopen code, you also can find the official code also configure that area to the default data:

So, next time, if it not work, you also can check the official code configuration.

Wish it helps you!

If you have the new question in the future, welcome to create the new question post!:)

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Kerry,

I have implemented and established SSP communication between LPC11U68 and LPC4367. But i am facing the issue while reading the data sent from LPC11u68 controller. Follwing are the details of the configuration of both the controller for communication.

LPC11U68:

Controller freq: 48Mhz, SSP Clock Rate: 1Mhz, Slave Mode , Mode 0

LPC4367:

Controller freq: 100Mhz, SPI Clock Rate: 1Mhz, Master Mode, Mode , Mode 0, SPI peripheral freq: 50Mhz

Now master controller is asking data to slave and slave is responding the data available. But here slave controller is recieving the data sent from master but master is not recieing the the data sent from slave to master in free running mode.

but when put delay while reading the data from slave then i recieve complete data expected. below is the code of reading at master side

Enable_CT_SS();

Chip_SPI_SendFrame(LPC_SPI,Tx_data);

while(!(Chip_SPI_GetStatus(LPC_SPI) & SPI_SR_SPIF)||(ul16_Timeout_count++ < timeout));

ul16_RxData = Chip_SPI_ReceiveFrame(LPC_SPI);

Disable_CT_SS();

Here it checks for SPI transmit flag and the timeout delay before reading the data. But if i remove the part from the master side then it recieves 0 and the data get sifted.

Please let me know the reason for the same since both controllers are running with different frequency . Also in SSP there is a provison of checking RX flag and TX flag but in SPI there is only one flag TX flag. When Slave transmit data it is in busy state but at the master side since the transmit flag is ok it reads the data and close the CS.

Kindly let me know the solution or the reason for the same.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Gaurav More,

Please send me your problem project, both the LPC11U68 and LPC4367 code, and also tell me the IDE you are using, then I will help you to check it on my side.

Waiting for your problem projects.

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kerry,

Please find attached code for SSP and SPI for your reference. I am using LPC11U68 and LPC4367 and using evaluation board for OM13058 for LPC11U68 and OM13088 for LPC4367. Editor is LPCEpresso V8.2.2_650. Kindly go through the code and let me know any further changes are required

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Gaurav More,

In your last email, you said:

LPC11U68:

Controller freq: 48Mhz, SSP Clock Rate: 1Mhz, Slave Mode , Mode 0

LPC4367:

Controller freq: 100Mhz, SPI Clock Rate: 1Mhz, Master Mode, Mode , Mode 0, SPI peripheral freq: 50Mhz

LPC11U68 is the slave, but why in your code, you configure it as master? Please check your attached LPC11U68 code:

Please check it again, did you meet the problem that when configure the LPC11U68 as master, and LPC4357 also the SPI master?

Please give me the clear goal, who is master, who is slave? Your problem is on the LPC11U68 or the LPC4357? If you have the problem SPI bus wave, please also set it to me.

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------