- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- LPCマイクロコントローラ

- :

- Problem caused by a difference between two demo board revision ?

Problem caused by a difference between two demo board revision ?

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

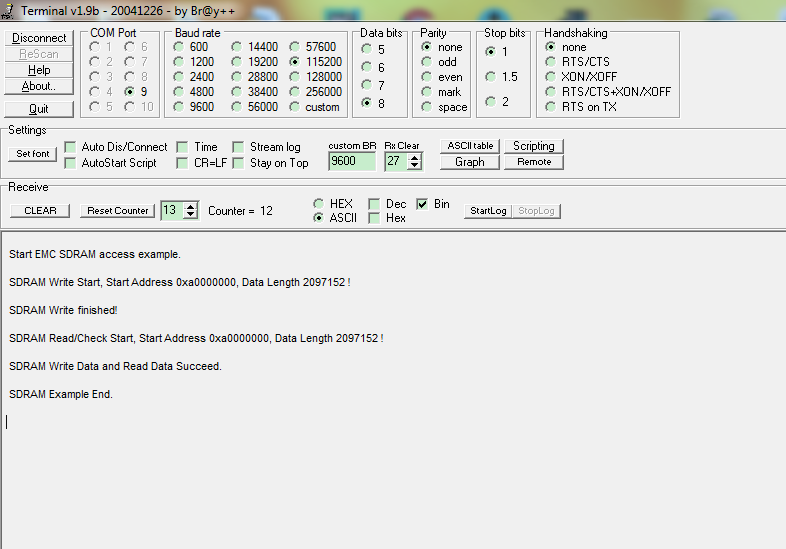

Hello,

I have a problem with the code example from a SDK from NXP about the EMC bus to use an external SDRAM. I use the LPCXpresso 546xx/540xx demo board from NXP.

The code example works correctly when I use the demo board LPCxpresso546xx/540xx with an external SDRAM from Micron ( MT48LC8M16A2B4) but when I use the demo board LPCxpresso546xx/540xx with an external SDRAM from Winbond (W9812G6JB-6I), the program says that there is an error when it checks the written data in the external SDRAM memory.

I was able to see in the memory that there is an error during data writing step :

Normally, the program writes (from the 0xA0000000 address) data from 0 and increasing each value by 1 compared with the previous value (ex : 00000000, 00000001, ...., 0000000A, 0000000B). However, at an address the written value is not correct compared with the others (ex : 000002FC, 000002FD, 000002FE, 6B836021, 00000300, 00000301, the wrong value is at the address 0xa0000bfc but at each try, the address with the wrong value is not the same).

Best regards,

Benjamin

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks for your reply.

I only have one rev E board on hand, it's LPCXpresso54018.

It doesn't encounter a similar error as you mentioned above when running the emc_sdram code.

I've also attached the BOARD_InitSDRAM() function below, please check it.

#ifdef W9812G6JB6I

#define SDRAM_REFRESHPERIOD_NS (64 * 1000000 / 4096) /* 4096 rows/ 64ms */

#define SDRAM_TRP_NS (20u)

#define SDRAM_TRAS_NS (42u)

#define SDRAM_TSREX_NS (72u)

#define SDRAM_TAPR_NS (18u)

#define SDRAM_TWRDELT_NS (12u)

#define SDRAM_TRC_NS (60u)

#define SDRAM_RFC_NS (60u)

#define SDRAM_XSR_NS (67u)

#define SDRAM_RRD_NS (12u)

#define SDRAM_MRD_NCLK (2u)

#define SDRAM_RAS_NCLK (2u)

#define SDRAM_MODEREG_VALUE (0x23u)

#define SDRAM_DEV_MEMORYMAP (0x09u) /* 128Mbits (8M*16, 4banks, 12 rows, 9 columns)*/

#endif

/* Initialize the external memory. */

void BOARD_InitSDRAM(void)

{

emc_basic_config_t basicConfig;

emc_dynamic_timing_config_t dynTiming;

emc_dynamic_chip_config_t dynChipConfig;

/* Basic configuration. */

basicConfig.endian = kEMC_LittleEndian;

basicConfig.fbClkSrc = kEMC_IntloopbackEmcclk;

/* EMC Clock = CPU FREQ/2 here can fit CPU freq from 12M ~ 180M.

* If you change the divide to 0 and EMC clock is larger than 100M

* please take refer to emc.dox to adjust EMC clock delay.

*/

basicConfig.emcClkDiv = 1;

/* Dynamic memory timing configuration. */

dynTiming.readConfig = kEMC_Cmddelay;

dynTiming.refreshPeriod_Nanosec = SDRAM_REFRESHPERIOD_NS;

dynTiming.tRp_Ns = SDRAM_TRP_NS;

dynTiming.tRas_Ns = SDRAM_TRAS_NS;

dynTiming.tSrex_Ns = SDRAM_TSREX_NS;

dynTiming.tApr_Ns = SDRAM_TAPR_NS;

dynTiming.tWr_Ns = (1000000000 / CLOCK_GetFreq(kCLOCK_EMC) + SDRAM_TWRDELT_NS); /* one clk + 6ns */

dynTiming.tDal_Ns = dynTiming.tWr_Ns + dynTiming.tRp_Ns;

dynTiming.tRc_Ns = SDRAM_TRC_NS;

dynTiming.tRfc_Ns = SDRAM_RFC_NS;

dynTiming.tXsr_Ns = SDRAM_XSR_NS;

dynTiming.tRrd_Ns = SDRAM_RRD_NS;

dynTiming.tMrd_Nclk = SDRAM_MRD_NCLK;

/* Dynamic memory chip specific configuration: Chip 0 - W9812G6JB-6I */

dynChipConfig.chipIndex = 0;

dynChipConfig.dynamicDevice = kEMC_Sdram;

dynChipConfig.rAS_Nclk = SDRAM_RAS_NCLK;

dynChipConfig.sdramModeReg = SDRAM_MODEREG_VALUE;

dynChipConfig.sdramExtModeReg = 0; /* it has no use for normal sdram */

dynChipConfig.devAddrMap = SDRAM_DEV_MEMORYMAP;

/* EMC Basic configuration. */

EMC_Init(EMC, &basicConfig);

/* EMC Dynamc memory configuration. */

EMC_DynamicMemInit(EMC, &dynTiming, &dynChipConfig, 1);

}Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Benjamin Hainaut ,

Thank you for your interest in NXP Semiconductor products and

for the opportunity to serve you.

Before answering the question, I was wondering if you can introduce the condition and steps of replicating the phenomenon, for instance, the demo boards, demo code, etc, as it will help me to figure it out.

Looking forward to your reply.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I use a LPCXpresso546xx/540xx revision E and for the test, I use the emc_sdram program from SDK_2.5.0_LPCXpresso54628.

Yesterday, I modified the specific time "SDRAM_TRP_NS" in the file "board.c" with the other specific times with the values given in the datasheet from Winbond. The error is again present but when I modify the SDRAM_TRP_NS value with higher value than value in datasheet, there is not error left.

Other interesting fact : when I set the frequency of the EMC bus to 110 MHz (after setting the AHB bus' clock to 220 MHz), the value given in datasheet (for SDRAM_TRP_NS) doesn't cause error anymore.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks for your reply.

I only have one rev E board on hand, it's LPCXpresso54018.

It doesn't encounter a similar error as you mentioned above when running the emc_sdram code.

I've also attached the BOARD_InitSDRAM() function below, please check it.

#ifdef W9812G6JB6I

#define SDRAM_REFRESHPERIOD_NS (64 * 1000000 / 4096) /* 4096 rows/ 64ms */

#define SDRAM_TRP_NS (20u)

#define SDRAM_TRAS_NS (42u)

#define SDRAM_TSREX_NS (72u)

#define SDRAM_TAPR_NS (18u)

#define SDRAM_TWRDELT_NS (12u)

#define SDRAM_TRC_NS (60u)

#define SDRAM_RFC_NS (60u)

#define SDRAM_XSR_NS (67u)

#define SDRAM_RRD_NS (12u)

#define SDRAM_MRD_NCLK (2u)

#define SDRAM_RAS_NCLK (2u)

#define SDRAM_MODEREG_VALUE (0x23u)

#define SDRAM_DEV_MEMORYMAP (0x09u) /* 128Mbits (8M*16, 4banks, 12 rows, 9 columns)*/

#endif

/* Initialize the external memory. */

void BOARD_InitSDRAM(void)

{

emc_basic_config_t basicConfig;

emc_dynamic_timing_config_t dynTiming;

emc_dynamic_chip_config_t dynChipConfig;

/* Basic configuration. */

basicConfig.endian = kEMC_LittleEndian;

basicConfig.fbClkSrc = kEMC_IntloopbackEmcclk;

/* EMC Clock = CPU FREQ/2 here can fit CPU freq from 12M ~ 180M.

* If you change the divide to 0 and EMC clock is larger than 100M

* please take refer to emc.dox to adjust EMC clock delay.

*/

basicConfig.emcClkDiv = 1;

/* Dynamic memory timing configuration. */

dynTiming.readConfig = kEMC_Cmddelay;

dynTiming.refreshPeriod_Nanosec = SDRAM_REFRESHPERIOD_NS;

dynTiming.tRp_Ns = SDRAM_TRP_NS;

dynTiming.tRas_Ns = SDRAM_TRAS_NS;

dynTiming.tSrex_Ns = SDRAM_TSREX_NS;

dynTiming.tApr_Ns = SDRAM_TAPR_NS;

dynTiming.tWr_Ns = (1000000000 / CLOCK_GetFreq(kCLOCK_EMC) + SDRAM_TWRDELT_NS); /* one clk + 6ns */

dynTiming.tDal_Ns = dynTiming.tWr_Ns + dynTiming.tRp_Ns;

dynTiming.tRc_Ns = SDRAM_TRC_NS;

dynTiming.tRfc_Ns = SDRAM_RFC_NS;

dynTiming.tXsr_Ns = SDRAM_XSR_NS;

dynTiming.tRrd_Ns = SDRAM_RRD_NS;

dynTiming.tMrd_Nclk = SDRAM_MRD_NCLK;

/* Dynamic memory chip specific configuration: Chip 0 - W9812G6JB-6I */

dynChipConfig.chipIndex = 0;

dynChipConfig.dynamicDevice = kEMC_Sdram;

dynChipConfig.rAS_Nclk = SDRAM_RAS_NCLK;

dynChipConfig.sdramModeReg = SDRAM_MODEREG_VALUE;

dynChipConfig.sdramExtModeReg = 0; /* it has no use for normal sdram */

dynChipConfig.devAddrMap = SDRAM_DEV_MEMORYMAP;

/* EMC Basic configuration. */

EMC_Init(EMC, &basicConfig);

/* EMC Dynamc memory configuration. */

EMC_DynamicMemInit(EMC, &dynTiming, &dynChipConfig, 1);

}Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Thank you for your answer, it works correctly.

The problem went from a wrong setting of the specific times (SDRAM_TRP_NS, SDRAM_TRAS_NS ect ...).

Have a nice day,

Benjamin