- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- Re: LPC8xx USART synchronous mode SCLK edge

LPC8xx USART synchronous mode SCLK edge

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

My question is about the USART module in the LPC8xx series microcontrollers. If the USART is transmitting in synchronous mode, does the signal transition on the rising or falling edge of SCLK, i.e. should the receiver sample it on the falling or rising edge of SCLK? I can't find this information in the User's Guide. The guide mentions CLKPOL (bit 12 in the USART config register), which determines the clock edge used by the receiver. Does this bit also affect the transmitter, or is there some other way of selecting the edge? If CLKPOL also affects the transmitter, I would assume the signal transition would happen on the opposite edge, so that similarly configured devices could communicate with each other.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Johan,

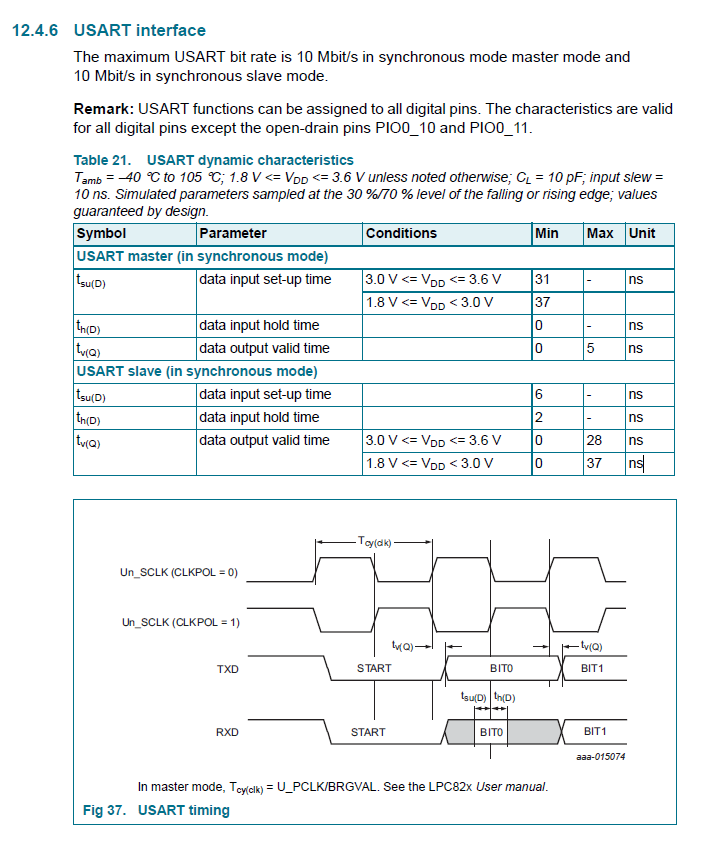

1. If the USART is transmitting in synchronous mode, does the signal transition on the rising or falling edge of SCLK,

You can find the according information in the datasheet.

You can find, when UART is transmitting, it still determined by the CLKPOL.

1. CLKPOL=0, rising is changing data, falling is acquiring data.

2. CLKPOL=1, falling is changing data, rising is acquiring data.

The USART timing is very clear.

Wish it helps you!

If you still have question, please let me know!

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Johan,

1. If the USART is transmitting in synchronous mode, does the signal transition on the rising or falling edge of SCLK,

You can find the according information in the datasheet.

You can find, when UART is transmitting, it still determined by the CLKPOL.

1. CLKPOL=0, rising is changing data, falling is acquiring data.

2. CLKPOL=1, falling is changing data, rising is acquiring data.

The USART timing is very clear.

Wish it helps you!

If you still have question, please let me know!

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your answer. Mmy fault, I didn't think of looking for this information in the data sheet, only the User Manual. The User Manual is incomplete: it does document the CLKPOL bit, but only for received data. It doesn't say that the CLKPOL bit also applies to transmitted data, or on which edge the data is safe to sample.

All is clear now, thank you once again for your help.