- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

LPC54608 Ethernet MDIO CSR clock range for 180MHz

I am using the LPC54608 evaluation board OM13092 and want to get Ethernet running using a system core clock of 180 MHz. The examples of the SDK2.2 use only 48 MHz system core clock.

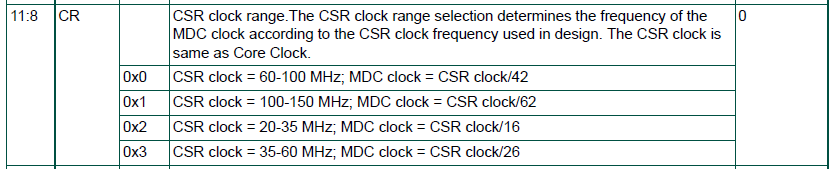

In the MAC_MDIO_ADDR register I have to select a CSR clock range (Bits 11:8). According to the user manual Rev2.0, I can set CSR values for clock ranges up to 150 MHz. How can I set a clock range for 180 MHz?

Best regards,

Holger

(Source: NXP UM10912 User Manual Rev. 2.0, Table 800)

P.S. The OM13092 uses a LAN8720 phy, which allows for a maximum MDC clock period of 400ns -> 2.5 MHz. If I would use the register value 1, I would get a clock of 180MHz / 62 = 2.9 MHz. Therefore I need the possibility to get a lower MDIO clock.

Why is this change not integrated in the latest SDK 2.6.

This issue was first delieverd to NXP from Holger Sachs end of 2017 and readressed by me May of 2019 and still this was not included in the SDK release from June 2019?

Will this never be integrated in the SDK?

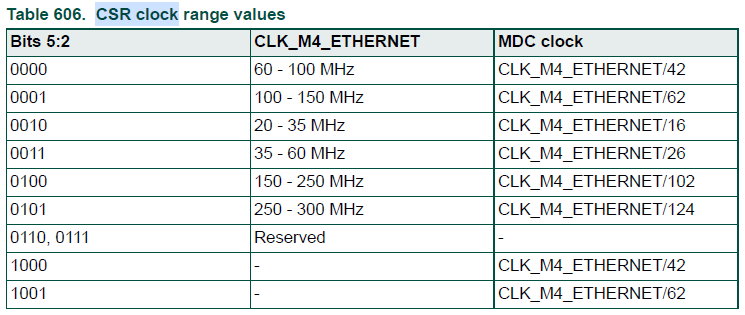

In the meantime I found out, that it is possible to use the value 0x4, which divides the core clock by 102. I found this value in the LPC43xx users manual (Rev 2.0, Table 606) and just gave it a try.

However:

Could anyone from NXP please give an official statement confirmation?

Please enahce your users manual with the next update.

Best regards,

Holger Sachs

Hi Holger Sachs,

TIC

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

That thread helped us as well,

but we need confirmation from NXP.

The newest user manual for LPC546xx, the UM10912 with version 2.2 from 29.10.2018, does not include the value 0x4 for the CR register as described above.

Also the fsl_enet - driver is therefore buggy as when a clock > 150Mhz is used, the default selected CR is 0.

In our example, we are running at 180Mhz and the MDC clock therefore is divided by 42 = 4.29 Mhz.

I agree with you! It is definitely not acceptable that NXP does not care about this issue!

@NXP: Please do your homework.

By the way: jeremyzhou from NXP always promises that they will care about such issues. In my case, so far they cared about none.

Hi Holger Sachs,

The below is the reply from the AE team, please check it.

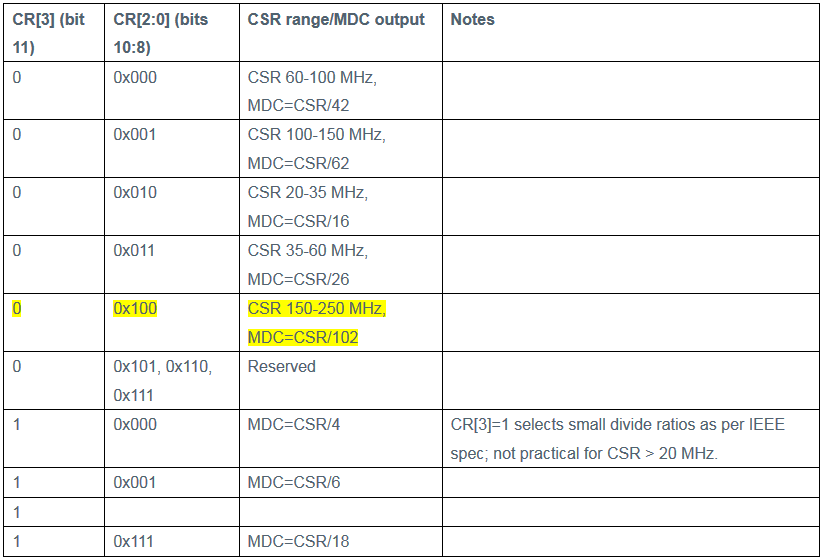

Below is summary of the full CSR clock range table. The UM is incomplete and will be updated in next revision. This update will be also applied to LPC54(S)0xx series.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

Hi Holger Sachs,

We both consider it should follow the same range rule as the below table shows, however, we need to contact the IP RD team for confirming.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------