- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- LPCマイクロコントローラ

- :

- LPC54606 UART FIFO - can't reset RXERR

LPC54606 UART FIFO - can't reset RXERR

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

LPC54606 UART FIFO - can't reset RXERR

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

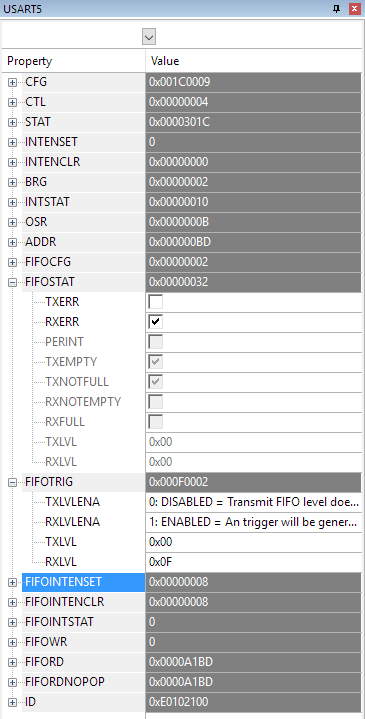

I'm unable to reset the RXERR-flag once it occurs.

clearing according to USART_TransferHandleIRQ() from USART driver version 2.0.3:

/* Clear rx error state. */

base->FIFOSTAT |= USART_FIFOSTAT_RXERR_MASK;

/* clear rxFIFO */

base->FIFOCFG |= USART_FIFOCFG_EMPTYRX_MASK;

RXNOTEMPTY, RXFULL, and RXLVL are changing to 0 and staying 0 after clearing rxFIFO. Executing "base->FIFOSTAT |= USART_FIFOSTAT_RXERR_MASK" in single step mode clears RXERR to 0, but one step later RXERR returns to 1. This even happens if the UART ist disabled before clearing. UART is idle and FIFO stays empty - RXERR = 1...

According to the manual, RXERR should only trigger if the FIFO overflows?! Disabling the rx-FIFO clears the flag, but on re-enabling RXERR appears again...

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I partly backported the fsl_uart.c from the latest SDK 2.9.0 (USART_TransferHandleIRQ() + USART_TransferSendNonBlocking()) and the problem seems solved. My crashing version is SDK 2.4.1.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Bjoern,

Found you any solution?

Because I have a SAME problem as you.

My environment

MCU: LPC54618J512BD208, IDE: Keil uVision

I don't use LPCOpen HAL or any else. I use my own reg access.

RXERR flag occured directly after enable FIFOCFG->ENABLERX.

RX pin is still in log.1 without change (IOCON is configured for UART5.RX).

WTF?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Sorry, I don't have a solution yet... And currently no time to provide an example that works on an evaluation board. For me this problem only occurs rarely directly after power up. Chances are ~ 1:25... If startup succeeds, the device runs 24/7 without problems with heavy UART-load... If you are able to find the reason, please share the solution...

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Bjoern,

Hope you are doing well.

Could you please confirm the example that you are working with from the SDK so that I may reproduce this behavior from my end. So that I may better understand what is occuring.

Best Regards,

Sabina

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Sabina,

I'm not using any of the examples. I modified the SDK for my own hardware. The UARTs are using the ringbuffer. The RXERR can be triggered by pausing and continuing the application. I attached some screenshots what happens in the ISR when I try to clear RXERR, single stepping through the ISR. The screenshots were made with an empty FIFO (RXLVL is 0 and stays 0).

Clearing does not always fail, but i have situations where the application is effectively blocked by the ISR trying to clear RXERR in an endless loop.

Best Regards,

Bjoern

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Bjoern,

I have attempted to reproduce this behavior with no luck. The SDK example that we have for ring buffer does not produce this type of error with the evaluation board that we have. I recommend to attempt to use the same structure for your application as the SDK and see if the problem can be reproduced. If not, I'd ask you to create an example that can be reproduced on our evaluation boards so that I can test it and see what is actually occurring.

Best Regards,

Sabina