- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- Re: LPC54605 Flexcomm clock question

LPC54605 Flexcomm clock question

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

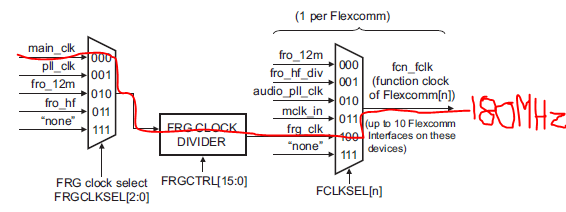

On the LPC54605J256 part, I am running the main clock at 180MHz. I'm configuring the SPI and I had a question about the clock configuration.

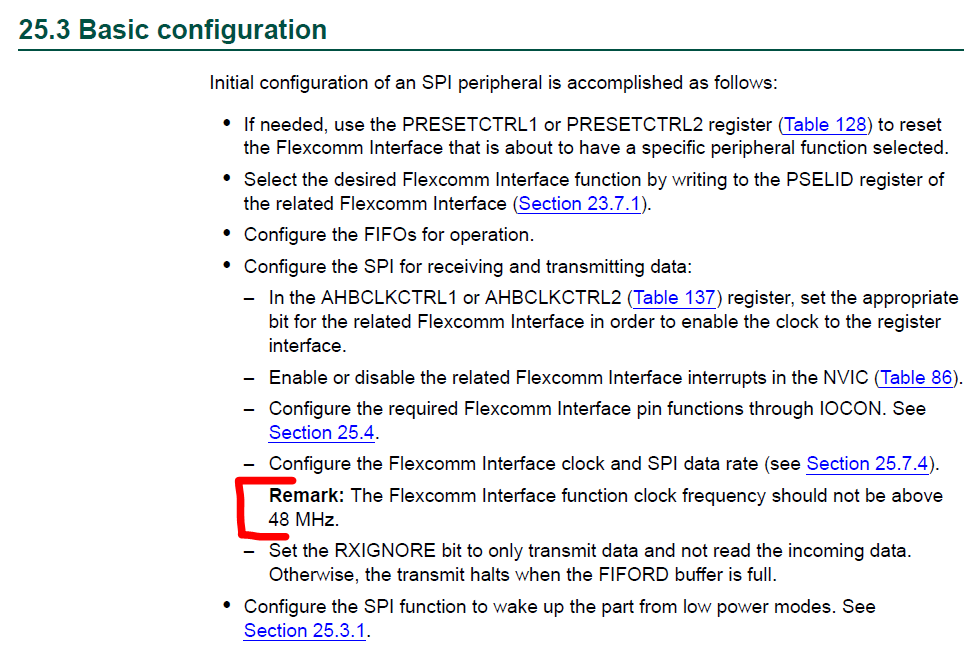

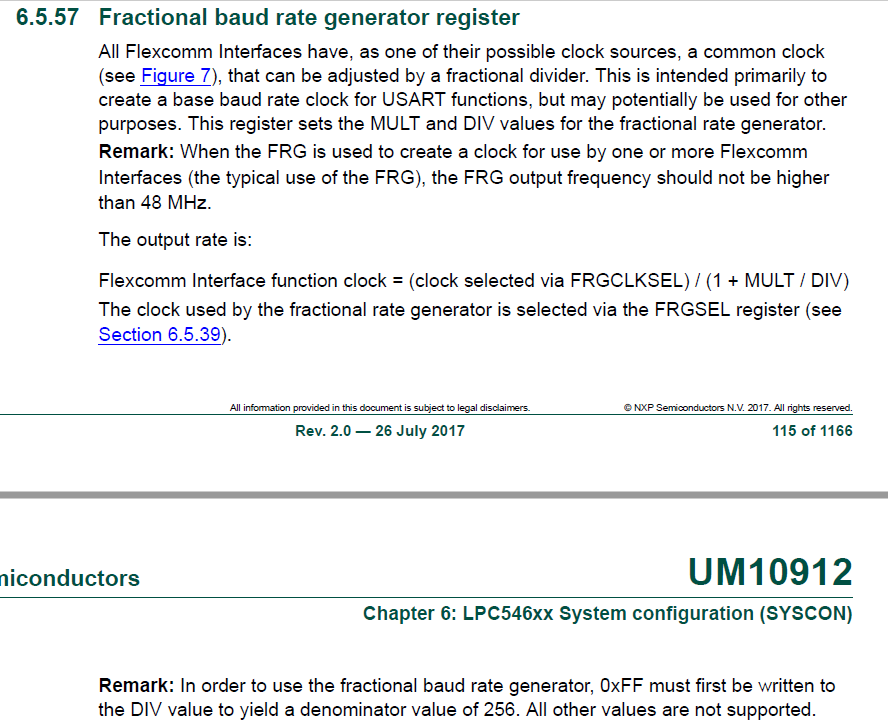

The datasheet says "Flexcomm Interface function clock frequency should not be above 48MHz". Since my main clock is 180MHz, I want to use the FRG for the common Flexcomm clock so I can use the FRGCTRL to divide the 180MHz down to the 30MHz clock I want.

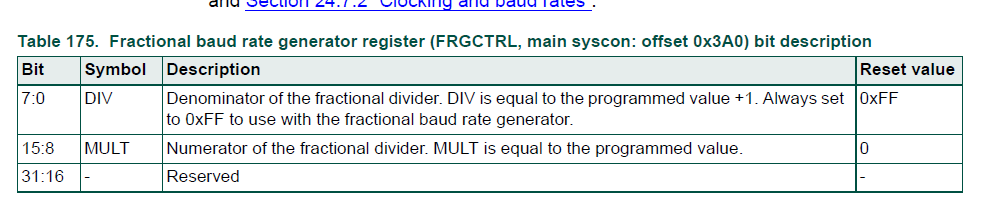

But, if I want to use a UART on another peripheral, the datasheet says the FRGDIV value must stay at 255. I can not achieve a clock of 30MHz with the FRGCTRL.

Flexcom Clock (30MHz) = 180MHz / (1 + MUL/256)

MUL would have to be 1280. Which can not fit in the MUL register.

My question is:

1) Can the input to a specific flexcomm (flexcomm0) be 180Mhz, then use the SPI0 DIV register to divide by 6 to get my 30MHz. Or does the clock before the SPI DIV have to be less than 48MHz to begin with?

My code is working with the frg_clk clock being 180Mhz and using the SPI DIV to bring it down to 30Mhz. But I want to make sure this is a valid operational mode.

End goal, I need the following to work:

Main clock = 180MHz

SPI0 (flexcomm0) = 30MHz

Flexcomm2 (UART) = 600Buad to 115200Baud

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Matt Lang,

Thank you for your interest in NXP Semiconductor products and

for the opportunity to serve you.

Q1)Can the input to a specific flexcomm (flexcomm0) be 180Mhz, then use the SPI0 DIV register to divide by 6 to get my 30MHz. Or does the clock before the SPI DIV have to be less than 48MHz to begin with?

-- The flexcomm interface's clock shouldn't be above the 48 MHz means that the clock before the SPI DIV has to be less than 48MHz to begin.

Hope this is clear.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can the Flexcomm interfaces use any of the crystal oscillator derived clocks for interface clock if main clock and pll clock frequency is over 48MHz and Audio PLL is not available? Are the FRO oscillators the only option then?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Matt Lang,

Thank you for your interest in NXP Semiconductor products and

for the opportunity to serve you.

Q1)Can the input to a specific flexcomm (flexcomm0) be 180Mhz, then use the SPI0 DIV register to divide by 6 to get my 30MHz. Or does the clock before the SPI DIV have to be less than 48MHz to begin with?

-- The flexcomm interface's clock shouldn't be above the 48 MHz means that the clock before the SPI DIV has to be less than 48MHz to begin.

Hope this is clear.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------