- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- Re: LPC1769 UART1 THRE interrupt

LPC1769 UART1 THRE interrupt

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LPC1769 UART1 THRE interrupt

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am having trouble understanding the exact conditions that will lead to a UART1 THRE interrupt on the LPC1769 as well as what we can infer from the THRE and TEMT bits being set in the U1LSR register.

What will lead to a THRE interrupt, is it just the fact that the Transmitter Holding Register (top byte of the FIFO) is empty? Or does it mean the whole FIFO, including the Transmitter Holding Register, is empty?

When I read U1LSR bit 5 (THRE), what can I infer from this? Does it mean that the FIFO is empty, or can it be that there are still bytes in the FIFO but not in the top byte (Transmitter Holding Register)?

When I read U1LSR bit 6 (TEMT), what can I infer from this? Does it mean that all scheduled bytes are transmitted or can it be that THR and TSR are empty but there are some bytes left in the FIFO.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Stephan,

Q1)What will lead to a THRE interrupt, is it just the fact that the Transmitter Holding Register (top byte of the FIFO) is empty? Or does it mean the whole FIFO, including the Transmitter Holding Register, is empty?

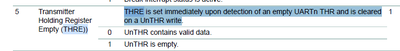

>>>>>THRE is set immediately upon detection of an empty UARTn THR and is cleared

on a UnTHR write.

Q2)When I read U1LSR bit 5 (THRE), what can I infer from this? Does it mean that the FIFO is empty, or can it be that there are still bytes in the FIFO but not in the top byte (Transmitter Holding Register)?

>>>It can be inferred that there are still bytes in the FIFO but not in the top byte, you can write the THR register.

Q3)When I read U1LSR bit 6 (TEMT), what can I infer from this? Does it mean that all scheduled bytes are transmitted or can it be that THR and TSR are empty but there are some bytes left in the FIFO.

>>> The TEMT is set when both UnTHR and UnTSR are empty; TEMT is cleared when

either the UnTSR or the UnTHR contain valid data. I mean that the THR, FIFO, TSR are all empty, the TEMT bit is set.

Hope it can help you

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Xiangjun,

Thanks for the quick reply, I have some additional questions.

1)

I cannot find an exact definition of "UART1 THR FIFO " in UM10360, it is used but never defined. What is exactly the scope of UART1 THR FIFO? I can find the definition of U1THR in section 15.4.2 "it is the top byte of the UART1 TX FIFO". Is UART1 THR FIFO a synonym for UART1 TX FIFO? How does it relate to figure 53 in section 15.5?

2)

Just to be sure, when I look at figure 53 of section 15.5, TEMT is set when "Transmitter Holding Register" (U1THR), "Transmitter FIFO" (UART1 THR FIFO?) and "Transmitter Shift Register" are all empty. So it cannot be the case that THR is empty, TSR is empty but there are bytes left in Transmitter FIFO?

Kind regards,

Stephan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Stephen,

1)The THRE of U1LSR:

A THRE interrupt is set immediately if the UART1 THR FIFO has held two or more characters at one time and currently, the U1THR is empty. The THRE interrupt is reset when a U1THR write occurs or

a read of the U1IIR occurs and the THRE is the highest interrupt (U1IIR[3:1] = 001).

For detailed inf, pls refer to section 15.4.5 UART1 Interrupt Identification Register (U1IIR - 0x4001 0008) in UM10360.

I copy it here:

"The UARTn THRE interrupt (UnIIR[3:1] = 001) is a third level interrupt and is activated

when the UARTn THR FIFO is empty provided certain initialization conditions have been

met. These initialization conditions are intended to give the UARTn THR FIFO a chance to

fill up with data to eliminate many THRE interrupts from occurring at system start-up. The

initialization conditions implement a one character delay minus the stop bit whenever

THRE = 1 and there have not been at least two characters in the UnTHR at one time

since the last THRE = 1 event. This delay is provided to give the CPU time to write data to

UnTHR without a THRE interrupt to decode and service. A THRE interrupt is set

immediately if the UARTn THR FIFO has held two or more characters at one time and

currently, the UnTHR is empty. The THRE interrupt is reset when a UnTHR write occurs or

a read of the UnIIR occurs and the THRE is the highest interrupt (UnIIR[3:1] = 001).

"

2)The TEMT bit of U1LSR:

TEMT is set when both UnTHR and UnTSR are empty; TEMT is cleared when

either the UnTSR or the UnTHR contain valid data.

When the TEMT bit is set, it means that both Transmitter FIFO and UnTHR are all empty.

Hope it can help you

BR

Xiangjun Rong

I