- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- LPCマイクロコントローラ

- :

- I2s In/out slave with SGPIO

I2s In/out slave with SGPIO

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

on a LPC4323 I have to implement two I2S ports (2 stereo input pairs) input and two I2S ports (2 stereo output pairs).

All I2S are slave ports, I mean they share the same BCLK (bit clock) and LRCK (left/right word sync) generated from an external master. I would use SGPIO pins.

Any suggestions for me? Can you suggest an example to start? Is it possible synchronize the SGPIO I2S ports with the I2S ports already available on LPC4323 and using both native I2S ports and emulated I2s via SGPIO?

thanks

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

There is no resource in SGPIO that would allow to synchronize to an I2S master. However, it is easily possible with the assistance of the SCT.

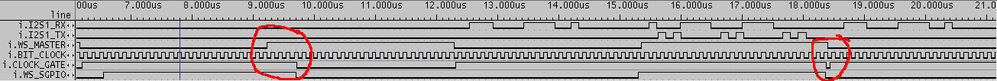

The idea is for SCT to monitor the internal state of the I2S slices, and gate the bit clock while SGPIO slices and the external I2S master are out of sync. The I2S bit clock goes to SGPIO, the I2S word select goes to SCT, and an external connection is required from an SCT output to an SGPIO pin to provide the clock qualifier function.

An SGPIO slice (slice J, SGPIO3) is configured to provide its own idea of the WS signal. It is connected to CTIN_0 of the SCT via the GIMA. A falling edge of the signal causes SCT to gate the SGPIO bit clock ("CLOCK_GATE"=0). SGPIO slices are now freezed in a known state. SCT monitors the master's WS signal, and reenables the bit clock ("CLOCK_GATE"=1) when it sees a falling edge there. Master and slave are now in sync, and the screenshot shows that no further clock gating occurs in the following frames. Synchronization only took one frame time.

The attached initialization file is not a complete project, but I hope you can get the idea from it. Data transfer is done in the SGPIO interrupt, and includes extracting the 24-bit samples (also the bit flipping due to SGPIO sending LSB first only).

Only two events are used in SCT, but two pins have to be used for connecting SCT to SGPIO.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Luke,

I suggest you to check the below application notes:

In addition, there is a software example using 4 SGPIO pins for a four channel I2S TX. Look in the folder \lpc43xx\Examples\SGPIO in this software package:

https://www.lpcware.com/content/nxpfile/lpc4350apdlzip

Have a great day,

Sol

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, thanks for your suggestions...

in my project one I2S port is the master and the other three are slaves, so I had some problems to define SGPIO slices to sync I2S 24bit data from the ADC/DAC of the slave ports with the I2S LRCK(WS) and BCLK(BCK) signals from the master one.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

There is no resource in SGPIO that would allow to synchronize to an I2S master. However, it is easily possible with the assistance of the SCT.

The idea is for SCT to monitor the internal state of the I2S slices, and gate the bit clock while SGPIO slices and the external I2S master are out of sync. The I2S bit clock goes to SGPIO, the I2S word select goes to SCT, and an external connection is required from an SCT output to an SGPIO pin to provide the clock qualifier function.

An SGPIO slice (slice J, SGPIO3) is configured to provide its own idea of the WS signal. It is connected to CTIN_0 of the SCT via the GIMA. A falling edge of the signal causes SCT to gate the SGPIO bit clock ("CLOCK_GATE"=0). SGPIO slices are now freezed in a known state. SCT monitors the master's WS signal, and reenables the bit clock ("CLOCK_GATE"=1) when it sees a falling edge there. Master and slave are now in sync, and the screenshot shows that no further clock gating occurs in the following frames. Synchronization only took one frame time.

The attached initialization file is not a complete project, but I hope you can get the idea from it. Data transfer is done in the SGPIO interrupt, and includes extracting the 24-bit samples (also the bit flipping due to SGPIO sending LSB first only).

Only two events are used in SCT, but two pins have to be used for connecting SCT to SGPIO.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Rolf, thanks for your helpful answer, I'll start from your code to solve my issue.