- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- FreeRTOS LCP55S69 i2c slave pull clock low

FreeRTOS LCP55S69 i2c slave pull clock low

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FreeRTOS LCP55S69 i2c slave pull clock low

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have FreeRTOS on LPC55S69 and use i2c in salve mode. As far as I know when master initiates a read over i2c and data on the slave is not ready, then the slave can pull low the clock until data gets ready then release it and let the master read it.

Is there a way to do this in FreeRTOS?

Is this possible when i2c slave NonBlocking mode is used?

Thanks,

Zoltan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi zoltan.balogh.eth@gmail.com,

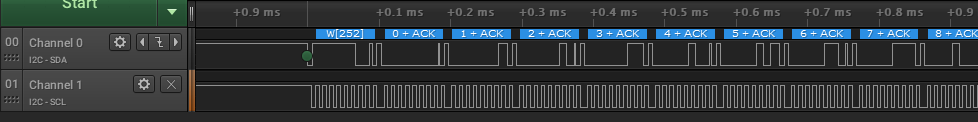

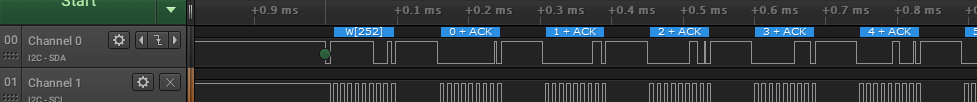

This delay is called clock streching and the I2C module of the LPC55S6x is capable of do it without software intervention, for example, this is a capture of the I2C signal using the freertos_i2x example from the SDK:

Adding a delay between transmissions will not affect the communication and the clock will stay low until the next transmission:

Best Regard,

Alexis Andalon

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi nxf46116,

Thank you for your reply! I still have some questions.

- In your capture the address + r/w bit is 252, which may mean master write to slave at address 0x7e. I don't know if it makes a big difference, but I was talking about master from slave read, when slave should keep the clock low as long as a buffer with data is not available.

- Where should the delay be added in the code? I guess not to he i2c slave callback, because of that's called from an ISR.

Best regards,

Zoltan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi zoltan.balogh.eth@gmail.com,

-The 252 (0x7E) is the slave address, not the address that will read the master.

-I added the delay in the FLEXCOMM4 IRQ, if you add a delay in the callback this will not affect the communication.

I hope this helps you.

Best Regards,

Alexis Andalon